DFX设计中有哪些bit文件?

DFX设计中有哪些bit文件?

Lauren的FPGA

发布于 2023-12-10 14:40:49

发布于 2023-12-10 14:40:49

DFX设计中有4类Bitstream文件,包括:

- Full configuration bitstreams

- Partial bitstreams

- Blanking bitstreams

- Clearing bitstreams

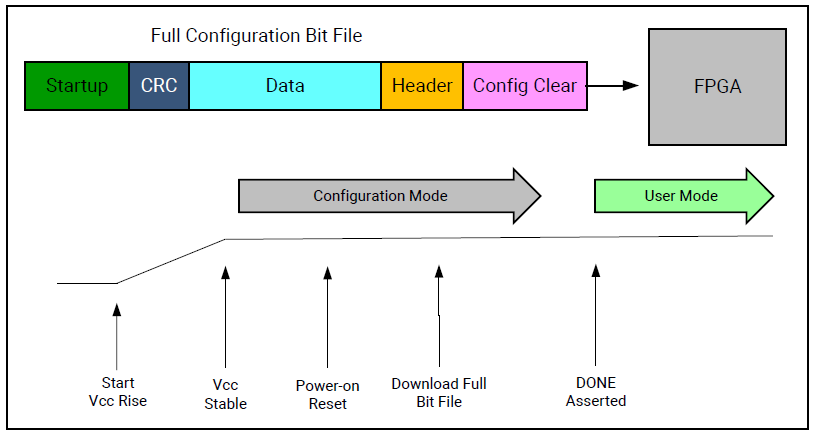

Full configuration bitstreams

Full configuration bitstreams对应的是静态区加动态区的完整设计,因此,该文件与传统的非DFX工程生成的bitstream从文件格式到文件结构均是一致的。同时使用方法也是一致的。另外,一些特征如对bitstream文件进行加密和压缩也是支持的。另一方面,这里的RP可以是黑盒子,即RP没有任何功能,这样可以最大程度缩减bitstream大小,如果再结合bitstream的压缩特性,那么就可以进一步提升FPGA初始配置时间。Full configuration bitstreams的加载过程如下图所示。加载完成且验证通过,DONE信号就会抬高,FPGA就进入用户模式,图中绿色标记。

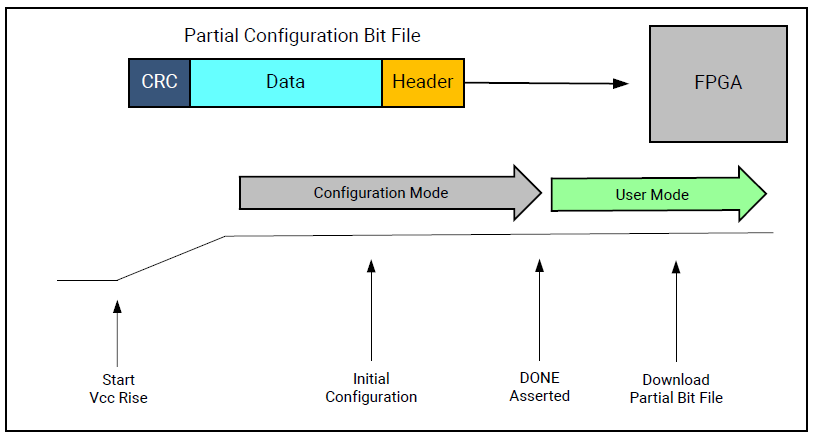

Partial bitstreams

当Full configuration bitstreams加载完成之后,就可以根据需要加载Partial bitstreams已切换动态区的功能,这正是DFX的本质。Partial bitstream有着和Full configuration bitstreams相同的文件结构,不同之处在于Partial bitstream仅针对FPGA指定区域也就是动态区。此外,针对DFX,Partial bitstreams还具有帧CRC检测和自动初始化(加载Partial bitstream后动态区可以进入已知状态)功能,同样也支持加密和压缩功能。Partial bitstream文件的大小和动态区的大小是成正比的,例如:RP大小是整个FPGA大小的20%,那么基本上Partial bitstream的大小也是Full configuration bitstream大小的20%。Partial bitstream是独立的,包含了地址、头、尾等具体信息,需要采用从模式加载如JTAG,Slave Serial或者Slave SelectMap,ICAP,PCAP(针对Zynq 7000 SoC)和MCAP(针对UltraScale和UltraScale+)。Partial bitstream可通过命令write_bitstream自动生成,也就是在生成Full configuration bitstream的时候会自动生成Partial bitstream文件,而无需额外操作。Partial bitstream的文件名也是有特定的规律的,假如

Full configuration bitstream文件为

- top_first.bit,

RP对应的Pblock名字为pblock_red,

那么Partial bitstream文件名就为

- top_first_pblock_red_partial.bit。

当FPGA进入用户模式时就可以加载Partial bitstream文件,如下图所示。对于UltraScale,在加载Partial bitstream之前先要加载Clearing bitstream,这时DONE信号为低,加载完Clearing bitstream之后,DONE信号依然保持低电平,之后加载Partial bitstream,完成之后DONE信号才会抬高。

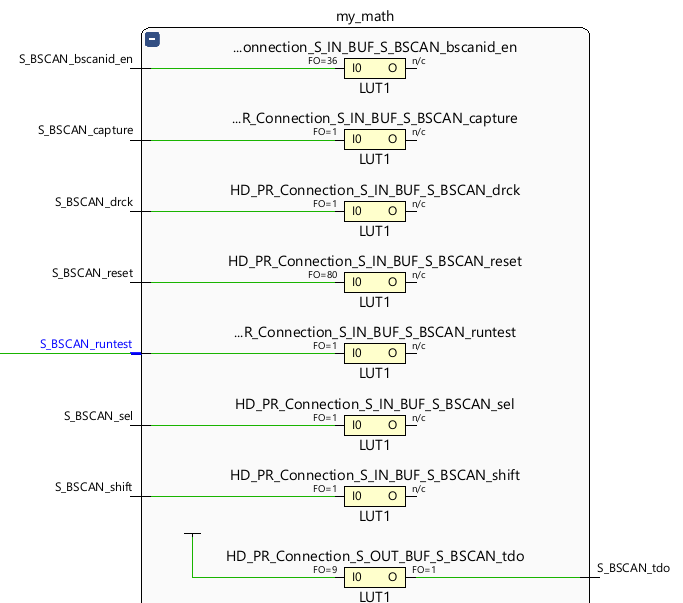

Blanking bitstream

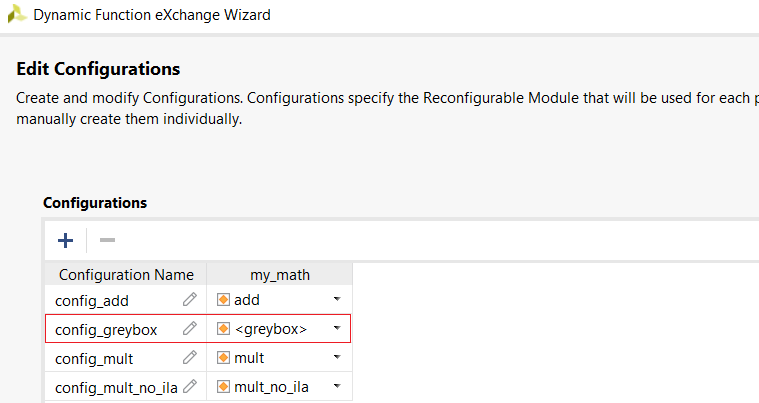

Blanking bitstream是一种特定的partial bitstream,它是在初始Configuration(静态区+完整动态区)的基础上,将静态区替换为黑盒子,同时将相应I/O插入LUT,这被称为会盒子(Greybox,注意和Blackbox是不同的)如下图所示。尽管这时动态区的逻辑功能已经被移除,但需要注意如果静态区要从动态区穿过也就是静态区使用了动态区的一些布线资源,那么这些布线资源仍然会被保留。

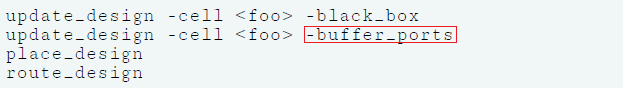

在Vivado图形界面方式下,可以很容易将动态区配置为Greybox,如下图所示。如果采用Tcl脚本则需要注意使用两次update_design命令,前者将动态区替换为Blackbox,后者对动态区相应I/O插入LUT。

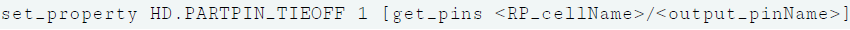

当对输出端口插入LUT时,默认情况下LUT输出为低电平,但可通过如下Tcl脚本修改其输出值,这里用到了属性HD.PARTPIN_TIEOFF。

Clearing bitstreams

Clearing bitstreams只是针对UltraScale芯片(不包括UltraScale+芯片),这是器件结构本身需求所决定的。Clearing bitstreams本身并不是Partial bitstreams,它只包含了动态区小于10%的Frame,因此其大小也就小于对应动态Partial bitstreams的10%。它需要和相应的Partial bitstream一起使用。例如设计中有一个RP,该RP下有两个RM,分别为RM1和RM2,那么就会生成两个Clearing bitstream文件:

- rm1_rp1_partial_clear.bit

- rm2_rp1_partial_clear.bit

也会生成两个Partial bitstream文件:

- rm1_rp1_partial.bit

- rm2_rp1_partial.bit

当由RM1切换到RM2时,先加载rm1_rp1_partial_clear.bit,紧随其后加载rm2_rp1_partial.bit。反之,由RM2切换到RM1时,需要先加载rm2_rp1_partial_clear.bit,再加载rm1_rp1_partial.bit。工具会自动生成Clearing bitstream文件,它和Partial bitstream文件的名字不同之处是在结尾多了“_clear”。

Copyright @ FPGA技术驿站

转载事宜请私信 | 获得授权后方可转载

本文参与 腾讯云自媒体同步曝光计划,分享自微信公众号。

原始发表:2023-12-07,如有侵权请联系 cloudcommunity@tencent.com 删除

评论

登录后参与评论

推荐阅读