Vivado使用小技巧

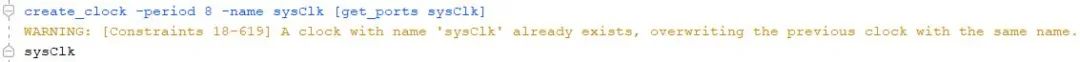

有时我们对时序约束进行了一些调整,希望能够快速看到对应的时序报告,而又不希望重新布局布线。这时,我们可以打开布线后的dcp,直接在Vivado Tcl Console里输入更新后的时序约束。如果调整后的约束在之前版本中已存在,那么Vivado会给出警告信息,显示这些约束会覆盖之前已有的约束;如果是新增约束,那么就会直接生效。例如,我们需要把时钟周期由10ns调整为8ns,就可以进行如下图所示的操作:

执行上述命令后,就可以重新生成时序报告了。需要说明的是这种方法只是用来快速查看时序报告以评估时序性能。如果把调整后的时序约束添加到工程中重新布局布线,得到的结果很有可能跟这种方式看到的不一样,这是因为布局布线本身是受时序驱动的。

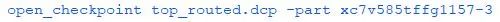

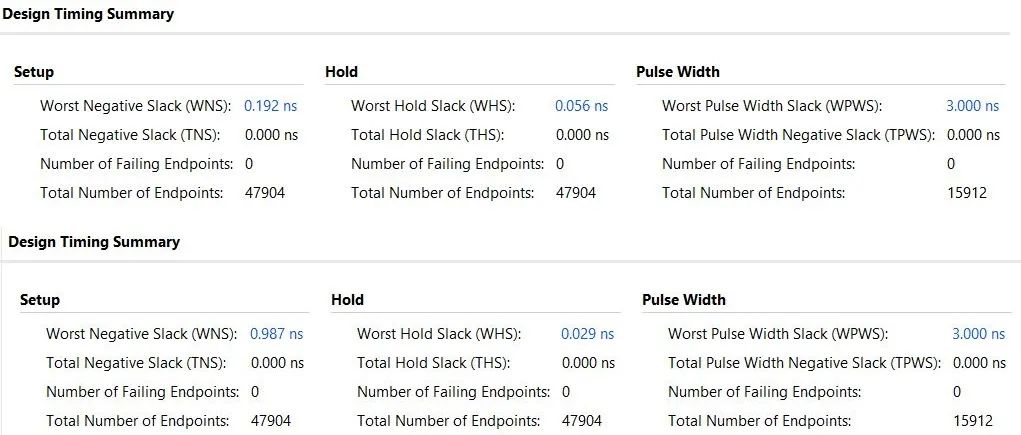

如何查看当前布线结果在更高速度等级芯片上的时序性能?

例如我们在速度等级为-2的芯片上完成了布局布线,需要进一步评估在速度等级为-3的芯片上时序裕量会有多大的提升,或者观察一下在速度等级为-1的芯片上时序能否收敛。这时我们只需用Vivado打开布线后的dcp,只是在打开dcp时选择芯片型号对应的速度等级为-3,其余封装保持不变,这需要借助Tcl命令open_checkpoint完成,如下图所示。在此基础上生成时序报告即可对比时序性能的变化。

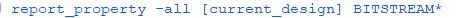

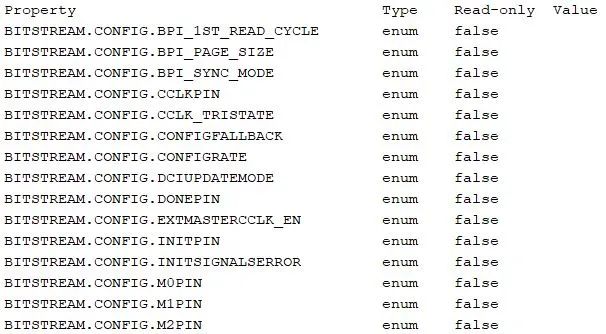

如何查看当前设计BITSTREAM属性信息?

可以使用如下Tcl命令生成BITSTREAM属性信息,需要打开布线后的网表文件。第1列为属性名,第2列为属性值的类型,第3列为属性是否只读,第4列为属性值。

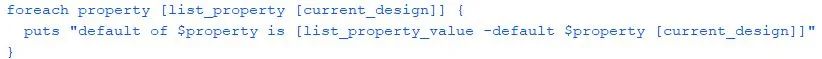

如果要知道属性的默认值,可采用如下图所示的Tcl脚本。

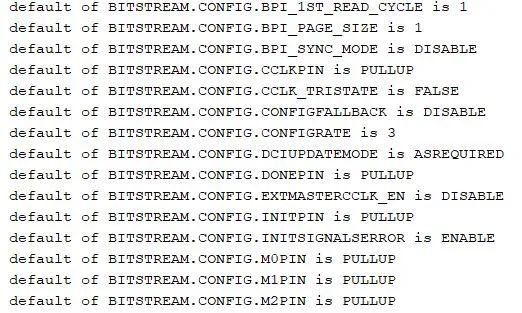

Vivado 2023.1 Pblock大小不合规报错怎么处理呢?

在Vivado 2023.1中,如果Pblock大小不合规就会报错,如下图所示。这其实是合理的,Vivado 2023.1及之后的版本都会如此处理。而2022.2及之前版本则不会报错,那是因为工具会自动进行调整,但这种调整只是保证Pblock大小合法,并不能保证一定符合用户预期。正因此,2023.1版本开始就更为严格了。

本文参与 腾讯云自媒体同步曝光计划,分享自微信公众号。

原始发表:2024-05-29,如有侵权请联系 cloudcommunity@tencent.com 删除

评论

登录后参与评论

推荐阅读