ESD耐压测试时,是否可能引发latch up现象?

原创ESD耐压测试时,是否可能引发latch up现象?

原创

斑图_Cyrus

发布于 2024-06-25 11:38:21

发布于 2024-06-25 11:38:21

这里先明白什么是latchup现象,在阐述闩锁效应之前,我们先看一下latch up概念。

定义:CMOS电路中,存在寄生的三极管PNPN,它们相互影响在VDD与GND间产生一低阻通路,形成大电流,烧坏芯片这就是闩锁效应(随着IC特征尺寸越来越小,集成度越来越高,闩锁效应发生的可能性越来越高;)

从定义中看到第一个词寄生的三极管pnp npn。下面看一下他们的工作原理,可以更好的理解latch up

三极管作用:作为电流控制管,他们最基本的作用就是放大电流作用。

开启条件

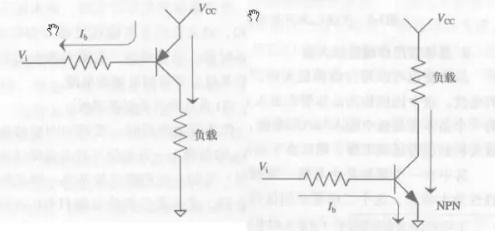

对于PNP三极管而言,如果要使PNP三极管导通,那么基极与发射极(发射结)正偏(Vbe=-0.7),即:基极(N)电势要比发射极(P)电势低,(这就是发射结正偏).还需要基极(N)电势要比集电极(P)电势高,(集电结反偏Vcb=-0.7).经典接法就是如图.

对于NPN三极管而言,如果要使NPN三极管导通,那么基极与发射极(发射结)正偏,即:基极(P)电势要比发射极(N)电势高,(这就是发射结正偏).还需要基极(P)电势要比集电极(N)电势低,(集电结反偏).经典接法就是如图.

导通放大状态

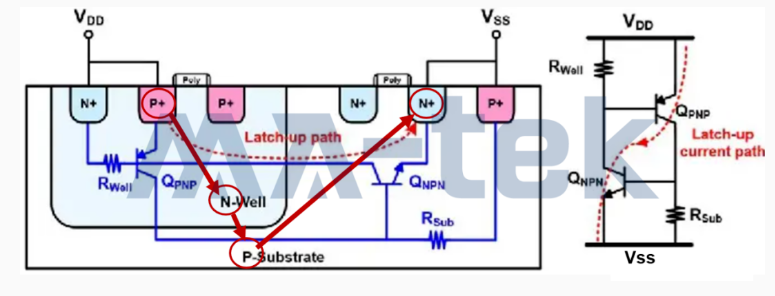

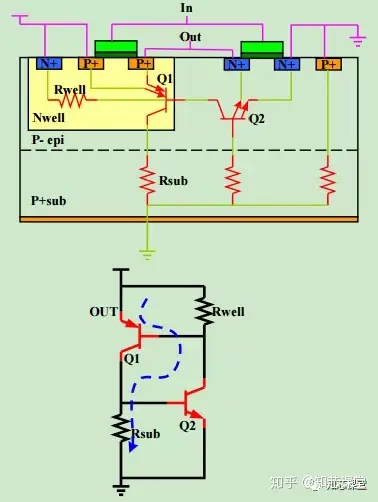

寄生图

Q1为一垂直式PNP BJT, 基极(base)是nwell, 基极到集电极(collector)的增益可达数百倍;

Q2是一侧面式的NPN BJT,基极为P substrate,到集电极的增益可达数十倍;

Rwell是nwell的寄生电阻,其值可以到20𝑘Ω;Rsub是substrate电阻,其值从数百到几欧姆。

QPNP和QNPN形成npnp结构,构成可控硅(Silicon-controlled rectifier: SCR)电路。

强电场、高电压或异常电流条件下,这些寄生结构可以被激活,从而引发latch-up现象

触发条件

- 当两个BJT都导通,在VDD和GND之间产生低阻抗通路;

- 两个晶体管反馈回路(feedback loop)增益的乘积大于1(𝛽1×𝛽2≥1)。

当无外界干扰未引起触发时,两个BJT处于截止状态,集电极电流是C-B的反向漏电流构成,电流增益非常小,此时Latch up不会产生。(漏电是一定存在的,只是大小的问题)

当其中一个BJT的集电极电流受外部干扰突然增加到一定值时,此时BJT的发射结正偏,电流反馈到另一个BJT,最终的反馈回路引起的电流需要乘以增益 𝛽1×𝛽2 ,此时为SCR的触发。从而使两个BJT因触发而导通,VDD至GND(VSS)间形成低抗通路,Latch up由此而产生。

如果( 𝛽1×𝛽2≥1 )满足,两个BJT将会持续产生高饱和电流,甚至在没有触发条件的时候。

集电极电流突增情况

在闩锁效应(Latch-up)现象中,寄生PNP晶体管的集电极会在受到外部干扰且基极到集电极电流增益达到一定值时出现大电流。

在高温下由于漏电升高,易触发寄生硅控整流器(Silicon Controlled Rectifier,SCR)启动而产生LU 效应,故可选择常温或高温(视产品规格的最大操作温度或者Tj 温度而定)两种测试环境,AEC 规范则是强制高温测试

当一个外部干扰(如电场、静电放电等)影响到晶体管的基极,使得基极与发射极之间的电压升高,寄生PNP晶体管的发射结将正偏。这导致发射区向基区注入大量空穴,这些空穴会扩散到集电区,被集电极收集,从而形成较大的集电极电流。由于PNP晶体管的基极通常是N阱,而集电极是P型衬底,当N阱与P衬底间的电压足够高时,即可引发上述过程。

芯片一开始工作时VDD变化导致nwell和P substrate间寄生电容(PN结电容)中产生足够的电流,当VDD变化率大到一定地步,将会引起Latch up。

• 当I/O的信号变化超出VDD-GND(VSS)的范围时,有大电流在芯片中产生,也会导致SCR的触发。

• ESD静电加压,可能会从保护电路中引入少量带电载子到well或substrate中,也会引起SCR的触发。

• 当很多的驱动器同时动作,负载过大使power和gnd突然变化,也有可能打开SCR的一个BJT。

• Well 侧面漏电流过大

防止latch-up方法

掺杂

使用重掺杂衬底,降低Rsub值,减小反馈环路增益。

使用轻掺杂外延层,防止侧向漏电流从纵向PNP到低阻衬底的通路。

版图设计时

- 多打接触孔,接触孔尽量靠近active有源区(降低Rwell,Rsub)

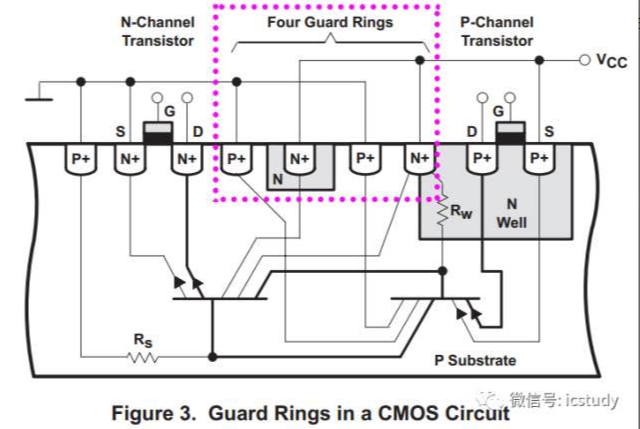

- 使用Guard ring(一方面降低Rwell,Rsub,一方面阻止载流子到达BJT基极)

- NMOS靠近GND,PMOS靠近VDD并保持足够距离,降低SCR触发的可能

使用Guardring:

1.多子GuardRing : P+ Ring环绕NMOS并接GND; N+ Ring环接PMOS并接VDD。使用多子保护环可以降 低Rwell和Rsub的阻值,且可以阻止多数载流子到基极。

2.少子GuardRing : 制作在N阱中的N+ Ring环绕NMOS并接VDD; P+ Ring环绕PMOS并接GND。 使用少子保护环可以减少因为少子注入到阱或衬底引发的闩锁

防止寄生晶体管EB结正偏,阻止起始电流的产生。例如输入电压超过VCC,EB结正偏就可能引起latch-up。

减小正反馈环路的增益。减小寄生晶体管的放大倍数和Rw/Rs阻值都可以有效降低环路增益。

这里列出一种常见的方法就是增加保护环,保护环有两种,

多子保护环可以减小Rw/Rs,

少子保护环可以收集少子,减小寄生晶体管的放大倍数β。

Vbe结 电路举例

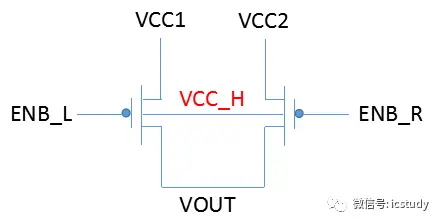

我们知道这两颗PMOS在CMOS工艺中是需要独立 N Well 的,

并且这个 N Well 的电位必须高于PMOS的源和漏(Drain/Source)以防止PN结导通。

那我们现在来为 N Well 选择电压(为了节省面积这两颗PMOS会放在同一个 N Well 中), 因为有时候VCC1大于VCC2,有时候VCC1小于VCC2,所以 N Well 不能用VCC1或者VCC2,而是 需要连接最高电位 VCC_H。

当电路从工作模式转入待机模式的时候,通常会对VCC_H进行放电discharge。假如VCC1、VCC2或者VOUT上面有很大电容,在进行discharge的时候VCC_H有可能低于VCC1、VCC2或者VOUT,引起PN结导通。在上面讲latch-up的时候我们已经知道VCC1、VCC2、VOUT可以看作是寄生PNP晶体管的发射极(E),VCC_H可以看作寄生PNP晶体管的基极(B)。PN结导通相当于EB结正偏,有可能引起 latch-up破坏电路。

面对潜在的 latch-up 风险,除了工艺上面通过掺金等减少少子存在时间的方法之外,我们还可以从 latch-up 的原理出来,用电路和版图的方法来解决。

(1)在电路设计过程中,我们可以通过减缓 VCC_H discharge的速度,让VCC_H始终高于其他电位。也可以增加VCC1、VCC2和VOUT的discharge path, 让PMOS的Drain/Source先于Well discharge。核心思想就是避免PN结导通(EB结正偏)。

(2)在版图实现过程中我们可以通过增加多子保护环(减小Rs/Rw)、少子保护环(减小寄生BJT的放大倍数)来减小寄生晶体管的环路增益。也可以让这个 N Well 远离其他电路来减小发生 latch-up 的风险。

用电路方法解决 latch-up 需要额外的控制电路,版图方法则是增加版图面积(往往这些PMOS的尺寸都很大,额外的版图面积就是钱啊)。至于到底采用哪种方法还是两者都采用,那就看实际项目情况吧。

最后再分享一个非常实用的验证技巧:

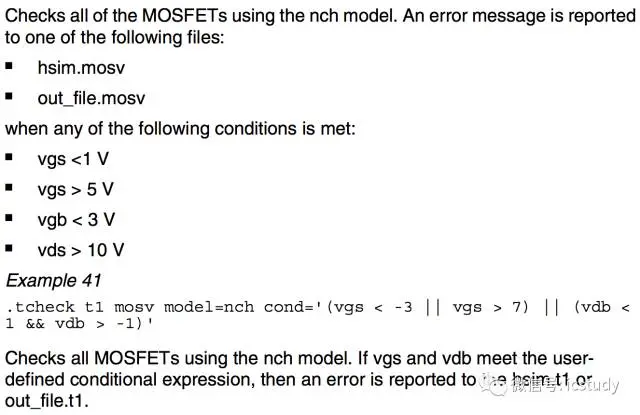

一般我们在电路设计的时候都已经花了很多力气来选择各个 Well 的电位,但是为了防止百密一疏,在仿真验证阶段还是要着重检查有没有PN结导通。某些电路仿真工具如HSIM可以监测MOS各端电压相对关系。如上图电路只要在testbench 中加入检查PMOS 的 Vsb、Vdb是否大于PN结正向导通电压的语句,就能检查出存在 latch-up 风险的电路模块。

ESD测试方法

假设芯片里具有AGND1、AGND2,DGND,AVCC1,AVCC2,DVCC,一般IO,这里以ALL to AGND1(+)为例说明如下:

第一步对所有的pin先量测一下IV 特性:

所有的电源和GND( 包括AGND1、AGND2,DGND,AVCC1,AVCC2,DVCC)全部接“地”,对一般IO加正反向电压,量测电流(一般MK2 機台default force I 量V如果要force V量I就要特別提出),如果是对某一电源或者“地”,则是其它剩余的所有电源和GND接“地”,然后对该电源或者GND加正反向电压,测量电流;

第二步对除了了AGND1 pin外,对所有的pin打正ESD脉冲;

第三步对打过正ESD脉冲的芯片所有pin重新量测一下IV特性,

方法应该和第一步相同(AGND1也要单独进行IV特性量测吗?此時並不會量AGND1的IV,因為它不是Zap的pin,除非在整個測完後另外单独进行IV特性量测,這也要另外提出有此需求);

第四步是对比

第一步和第三步量测的IV特性,如果某一pin的IV特性偏差前后差别超过30%,即认为该pin ESD fail(這裡是指IV Curve 超過判定標準,依規範定義還必須經過DC參數及功能測試來做最後判定,大部分客戶還是會依IV FAIL 來做分析及改善)

在进行ESD耐压测试时,可能会引发latch up现象。Latch-up是一种CMOS电路中特有的寄生效应,可能导致电路失效,甚至烧毁芯片。具体解释如下:

- ESD测试与Latch-up的关系

- 静电放电影响:ESD测试通过模拟静电放电的过程,对集成电路施加高电压。这些高电压脉冲可能穿透芯片内部的保护结构,并触发latch-up现象。

- 测试标准与方法:HBM(Human Body Model)和CDM(Charged Device Model)是两种常见的ESD测试模型。这些模型使用特定的测试仪器,如MK2测试仪,来模拟和施加高压应力。

- 测试结果分析:ESD测试报告中常包含pre-stress和post-stress的I-V曲线。如果测试后曲线与测试前差异超过30%,则视为失效。这种失效有可能就是由latch-up引起的。

- Latch-up的测试方法

- 电流测试:主要包括正电流测试(灌入电流)和负电流测试(拉电流)。这些测试通过对IO施加高压,检测是否有异常电流产生。

- 电压测试:主要是针对供电引脚进行过压测试,观察在最大运行电压下芯片的表现。

- 环境温度设定:常温或高温环境下进行测试,因为高温更易触发latch-up现象。

- ESD测试中的Latch-up触发风险

- 高电压穿透:ESD测试中施加的高电压可能穿透保护结构,直接触发latch-up所需的寄生结构。

- 电流异常波动:测试过程中电流的急剧变化也可能激活寄生三极管,导致latch-up现象。

- 设备与环境因素:测试设备的准确性和测试环境的稳定性也会影响latch-up的发生概率。

- 案例分析与预防措施

- 实际案例:许多集成电路在ESD测试后出现永久性损坏,多数是由于未采取有效的latch-up防护措施。

- 设计优化:在设计阶段考虑latch-up防护,如增加保护二极管、减小寄生电阻等措施。

- 测试方案调整:合理规划测试方案,逐步增加测试电压,同时监控电流变化以预防latch-up发生。

综上所述,ESD耐压测试确实存在引发latch-up现象的风险。这主要是由于高电压脉冲可能激活CMOS电路中固有的寄生结构,形成低阻抗通路并导致大电流持续流过。因此,在设计和测试阶段采取适当的防护措施至关重要,以确保电路的稳定性和可靠性。

深度解析:集成电路ESD防护、闩锁效应的测试方案及失效验证流程 - 半导体/EDA - -EETOP-创芯网

闩锁效应(Latch-up)详解 - 知乎 (zhihu.com)

LatchUp测试详解_专业集成电路测试网-芯片测试技术-ic test (ictest8.com)

原创声明:本文系作者授权腾讯云开发者社区发表,未经许可,不得转载。

如有侵权,请联系 cloudcommunity@tencent.com 删除。

原创声明:本文系作者授权腾讯云开发者社区发表,未经许可,不得转载。

如有侵权,请联系 cloudcommunity@tencent.com 删除。

评论

登录后参与评论

推荐阅读

目录