绝缘涂层键合金线

随着半导体行业继续向更高的引脚(Lead Finger)、更细的间距、多排接合焊盘和多堆叠芯片器件发展,通过引线键合的互连成为当今半导体封装工艺的挑战。泰丰瑞电子开发了绝缘涂层键合线(金线和铜线)。

可以实现复杂的封装设计,提高封装性能,提高高密度封装的成品率。本文概述了基于绝缘涂层键合线的涂层技术,以及相关辅助封装和设计技术。绝缘涂层键合金线的材料设计考虑及其性能,以及封装和组装考虑也将得到解决。

一/ 简介

绝缘涂层键合金线

长期以来,绝缘涂层键合线一直是高输入/输出(I/O)密度引线键合应用所追求的,过去的许多尝试都取得了有效成功。一种新型的键合线,即绝缘涂层键合线,为利用现有的基于引线键合的基础设施提供了具有成本效益的方法,以应对ITRS路线图概述的挑战。

以下部分概述了绝缘涂层键合线实施的基本要求:

1. 绝缘涂层材料的原则和性能考虑,形成的绝缘涂层称为绝缘涂层键合线

2. 融入的现有的组装基础设施(引线键合机、等离子设备、成型设备等)

3. FAB和金属化合物的形成

4. 第二焊点(引线键合)的可焊性

讨论扩展使用绝缘涂层键合线的封装相关设计和绝缘涂层键合线功能,包括产能提升和新的封装设计,并提供初步可靠性评估数据。

绝缘涂层键合金线

二/ 绝缘涂层键合金线的选材

绝缘涂层键合金线

“ 以下是绝缘涂层键合金线考虑的四个关键领域: ”

“1 /应用考虑因素(性能要求) ”

1. FAB形成 , 第二焊点可焊性(能够穿过涂层粘合)

2. 绝缘强度足够高,以便在设备应用电压下(Eg=5V工作电压)绝缘性

3. 高抗裂性和对裸金线的附着力,以防止键合过程中涂层的剥落,良好EFO烧球

4. 涂层后的裸金线的变化最小(如延展率,抗荷载能力等)

5. 耐低级和二级封装过程中可能使用的普通溶剂(如醇类,丙酮和DI水)

6. 能够在短时间内耐受高达300℃的温度(例如在无铅工艺所用的260℃回流温度下耐受10-15s)

“2 /物理和化学性能”

涂层材料中离子含量低(低于20ppm)

“3 /基础设施”

使用现有的行业标准设备(如引线键合机)

“4 /环境因素”

在形成FAB过程中,低挥发性有机化合物(VOC)

绝缘涂层键合金线

绝缘涂层键合线是为满足ITRS 未来应用对超细,高I/O密度应用的要求而设计的。当前绝缘涂层键合线生产的最大电压是5v。该规范涵盖了大多数中高数字集成电路应用。

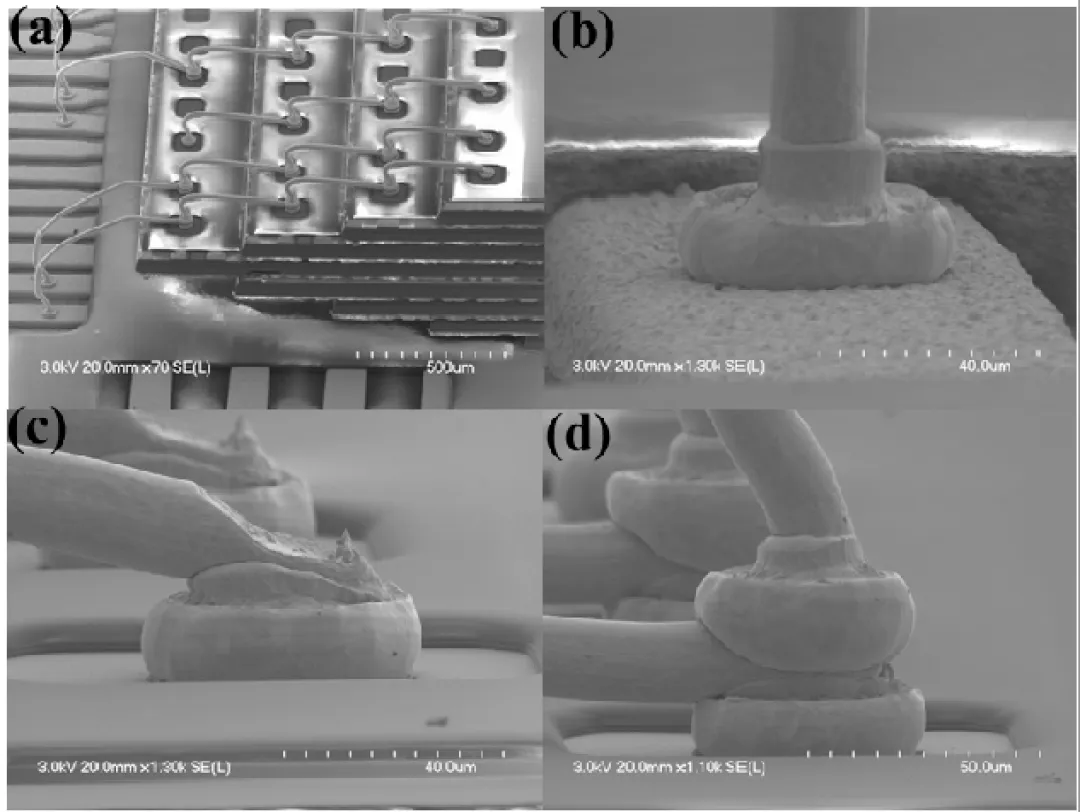

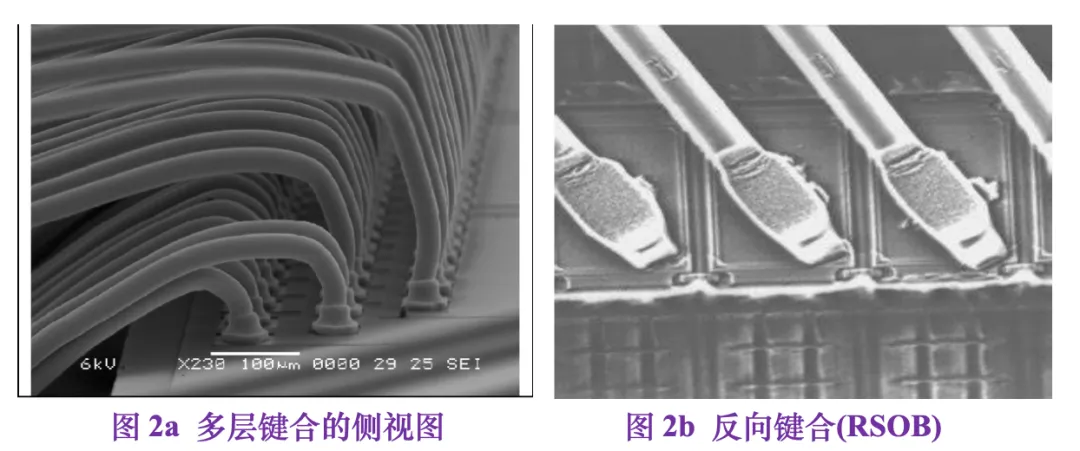

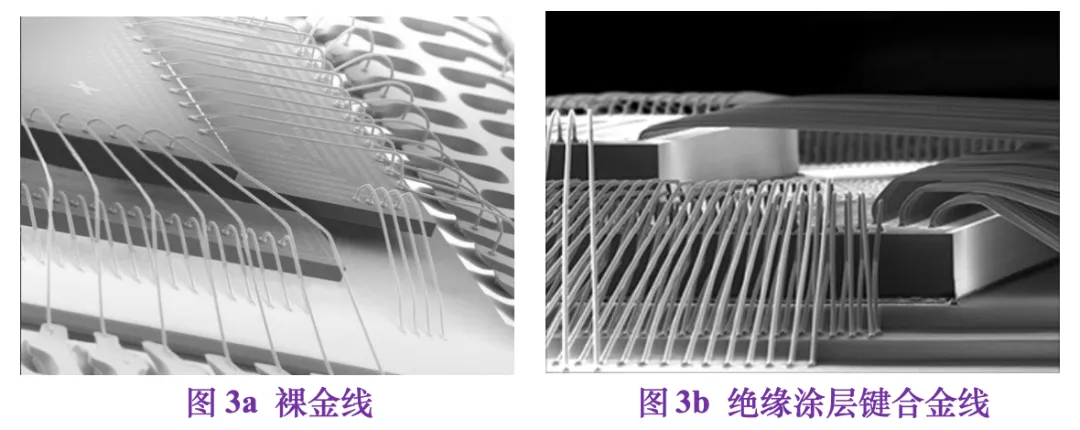

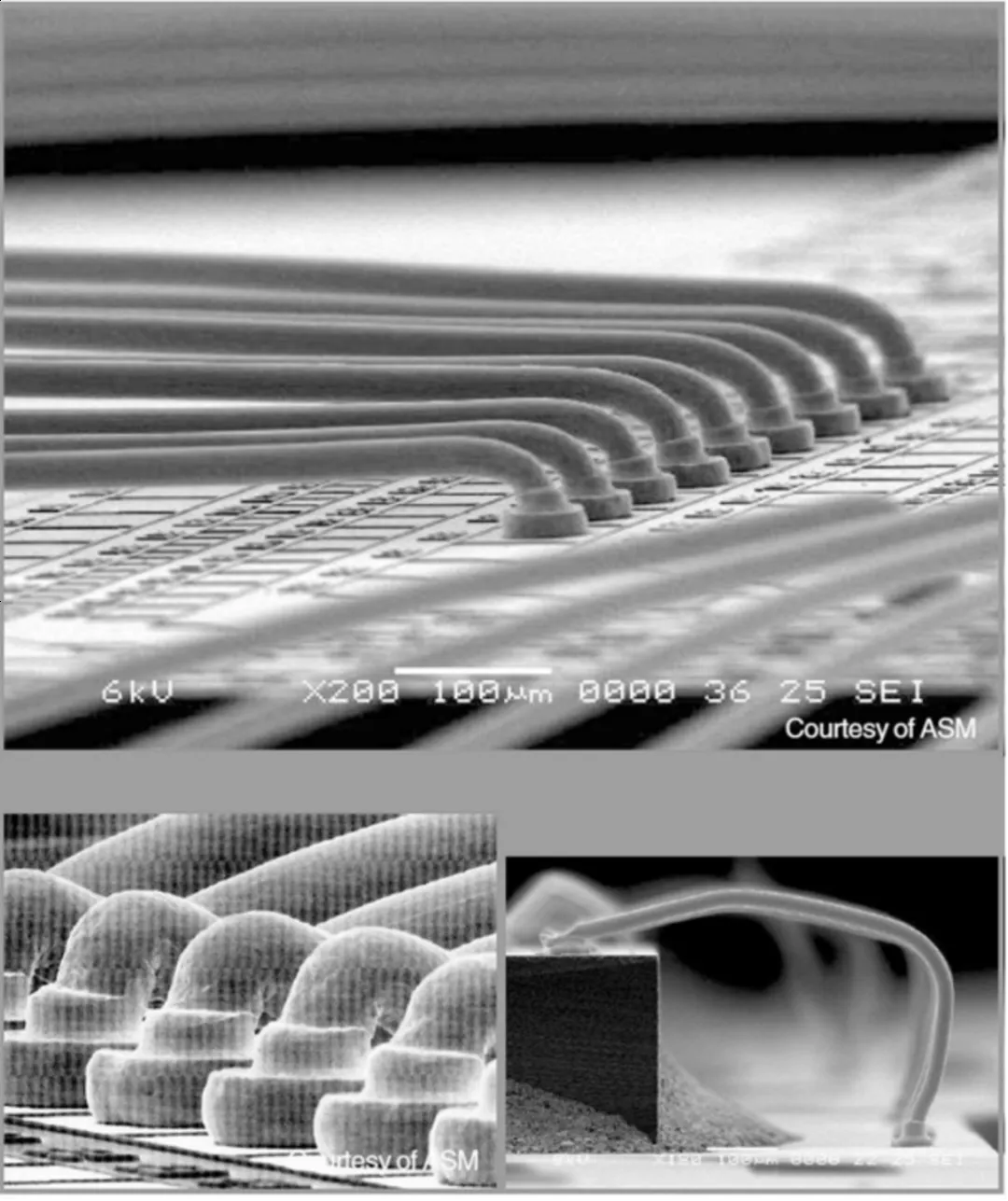

绝缘涂层键合线能防止键合线接触短路,从而提高器件成品率。具体来说,在芯片塑封过程中扫线一直是PBGA封装高密度互连的挑战。绝缘涂层键合线允许交叉和碰线,不论是任何原因或转移成型引起的碰线。这种性能有助于实现性应用,例如芯片倒装键合(图1 ) 。 多层堆叠芯片(Die Stack 图2a,图2b) ,系统级封装(SIP), P-O-P封装,多层引线键合(如图3)和矩阵键合应用。

绝缘涂层键合金线

图片

图1: 绝缘涂层键合线进行芯片间(Chip-to-Chip)键合

绝缘涂层键合线进行芯片间(Chip-to-Chip)键合,芯片间的(TSV)互连,有可能提高了设备的高速性。

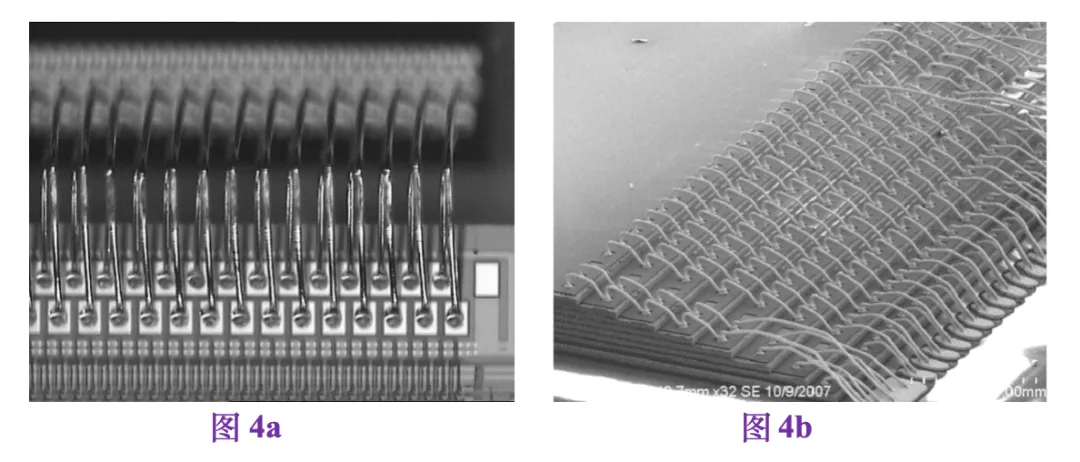

图4显示了芯片中键合线相互交叉和碰线的示例。可以直接使芯片间(Chip-to-Chip)的引线键合来实现关键布线,以实现芯片间最小化的延迟,这可以优化封装的电气性能。

图片

图 2 : 多层堆叠芯片引线键合

图片

图 3 : 高密度引线键合

图片

图 4 : 使用绝缘涂层键合线相互交叉的示例

裸线须小心间隔,至少相隔一根线径的距离,以防止短路。然而,绝缘涂层键合线可以相互接触而不会短路,从而增加布线密度和灵活性。

绝缘涂层键合金线

三/ 使用绝缘涂层键合金线键合

绝缘涂层键合金线

为实现更大的布线密度,涂层厚度必须足够薄,以使绝缘涂层键合线不须增加劈刀孔径,实现与相同直径的裸线焊盘(BPP)间距。此外,绝缘涂层键合线不应留下污染物(芯片/基板表面)和劈刀尖端的残留物,或在EFO形成过程中不挥发有害气体。

图片

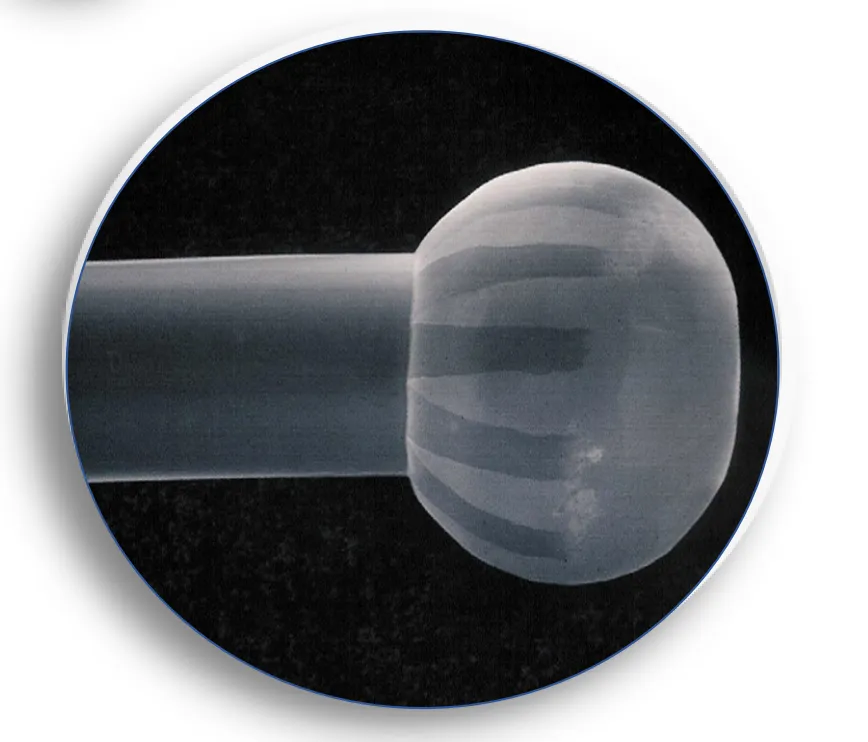

图 5 : 绝缘涂层键合线(FAB)上形成类似“西瓜条纹”的涂层

注意FAB底部无绝缘涂层

绝缘涂层键合线的第一焊点的可键合性形成取决于形成“西瓜条纹”对FAB的能力。在EFO球形成过程中,涂层在球的中间部分分裂成独特的西瓜条纹(图5),FAB的下半部分无绝缘涂层,涂层材料不会融化。

图片

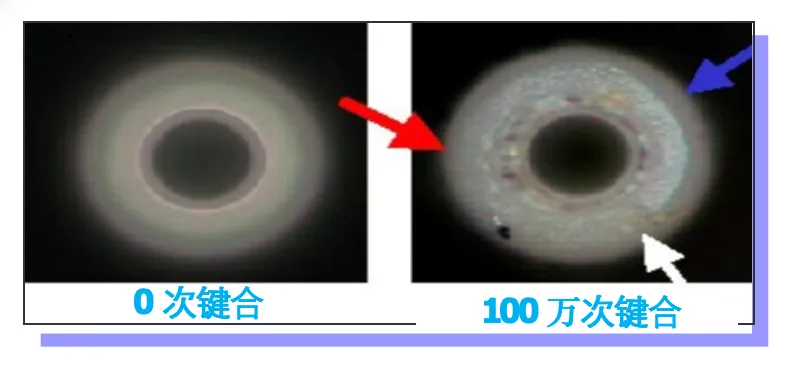

图 6a : 劈刀尖端残留物的键合前后检查

100万次键合前(左)和后(右)劈刀残留物的低倍图

图片

图 6b : 劈刀尖端残留物的键合前后检查

100万次键合后劈刀残留物的聚集放大视图

图片

图 6c : 1,00万次键合的侧面图,劈刀从不同角度观察图

图 6 : 劈刀检查前后

经过100万次键合后,劈刀显示的可忽略的涂层材料积累量(图6a和图6b)。图6a是标准SPT劈刀在0次键合后的图像,使用绝缘涂层键合线的相同劈刀尖端残留物在100万次键合后观察发现,经过100万次的键合后,劈刀尖端显示无任何残留物。图6b是图6a中劈刀尖端残留物的高倍放大视图,显示从焊盘上粘附的少量残留物。图 6c中显示的是1,00万次键合的侧面图,劈刀从不同角度观察图。

根据EPA测试方法TO-17,对引线键合过程中挥发的有机化合物(VOC)排放的室内空气质量进行了监测。EPA TO-17测试是将空气采样到吸收管中进行热吸收,并用质量选择(MS)和常规气相色谱(GC)检测分析。使用吸收剂从两个采样位置采集空气样本,一个靠近键合头(Bond Head),另一个面向操作者。经过实验两个样品都表明,所测定的所有有挥发性有机化合物都远远低于EPA标准所定义的标准。

图片

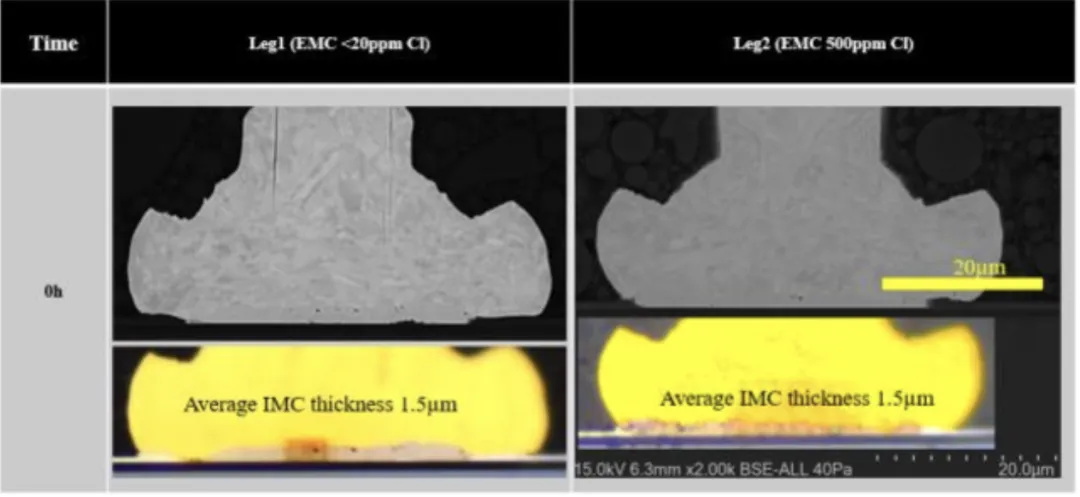

图 7 : 利用绝缘涂层键合线和裸线在0时刻形成金属化合物对比

样本显示超出75%的IMC在零时形成

图7显示了0时刻在绝缘涂层键合线底部的硝酸溶液中腐蚀时形成的键合球的2幅光学图像。绝缘涂层键合线与第一焊点形成的金属化合物(IMC)的覆盖率,暗区显示为深色区域,并计算了每个图像的暗区覆盖百分比。本文中使用的芯片焊盘上的铝金属化合物厚度约0.7微米,其中1%为硅,0.5%为铜。所有键合线的IMC在 0时刻观察到的键合数值大于75%的覆盖范围。

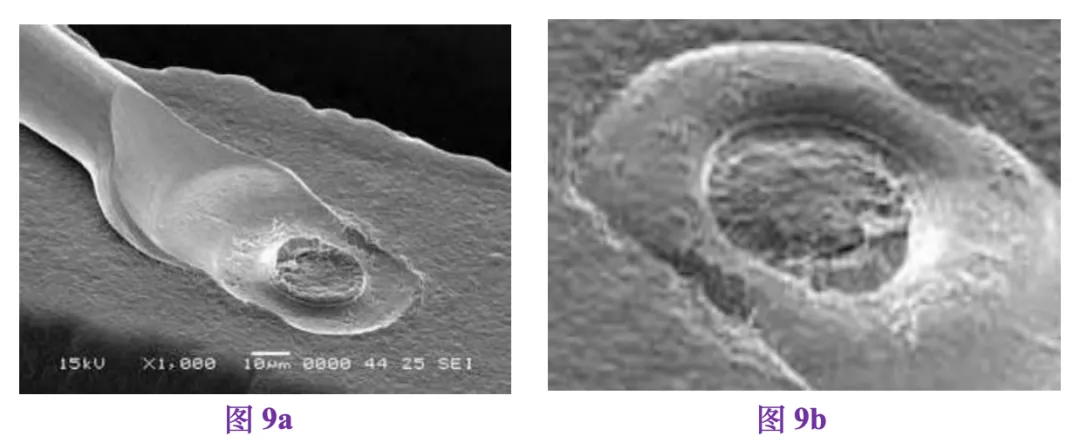

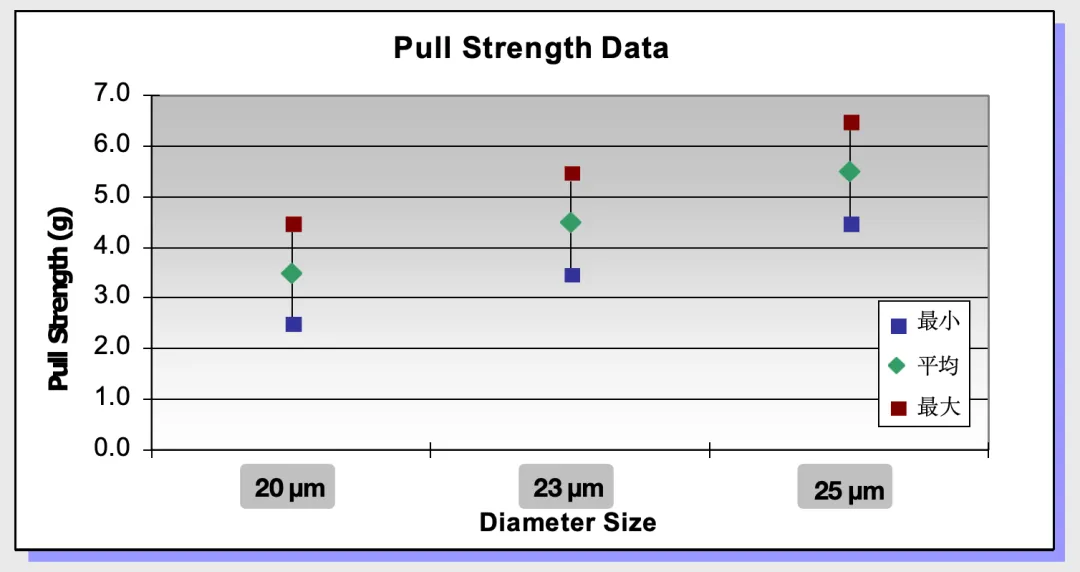

第二焊点键合(通常称为引脚键合),使用绝缘涂层进行键合,并采用当前标准的热超声引线键合机。对于绝缘涂层键合线与裸线相比,第二焊点需要不同的键合参数才能使绝缘涂层破裂,在标准键合参数范围内,但与裸线相比可能会发生变化。通常,绝缘涂层键合线的键合拉力强度略低。绝缘涂层键合线相对于裸线来说,图8和图9分别显示了引线键合拉力试验前和试验后引线键合的SEM图像,显示引线键合区域良好的键合情况。图10显示了绝缘涂层键合线用引线键合机(KS&8028)对3种不同线径(20、23、25μm)的绝缘涂层键合线进行键合,每种线径都键合在PBGA层压基板上。绝缘涂层键合线直径在PBGA层压基板上显示出可接受的拉力强度(如图10)。

图片

图 8:绝缘涂层键合线的第二焊点扫描电镜图像

图片

图 9 : 拉力试验前和试验后引线键合的SEM金属残留图像

图片

图 10 : 绝缘涂层键合线20μm、23μm、25μm三种不同线径的拉伸强度数据

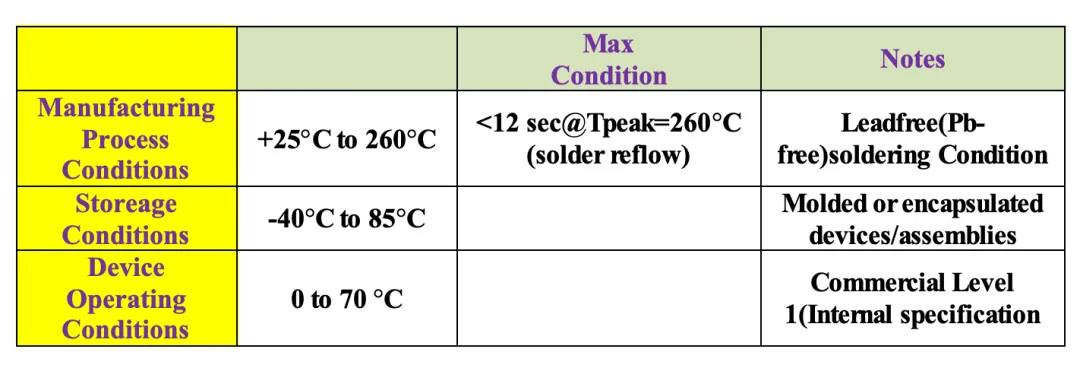

绝缘涂层键合线的可靠性 最新一代的(绝缘涂层键合线设计用于生产、存储和设备操作条件如表1

图片

表 1: 绝缘涂层键合线的应用:制造、存储和设备运行条件、温度范围

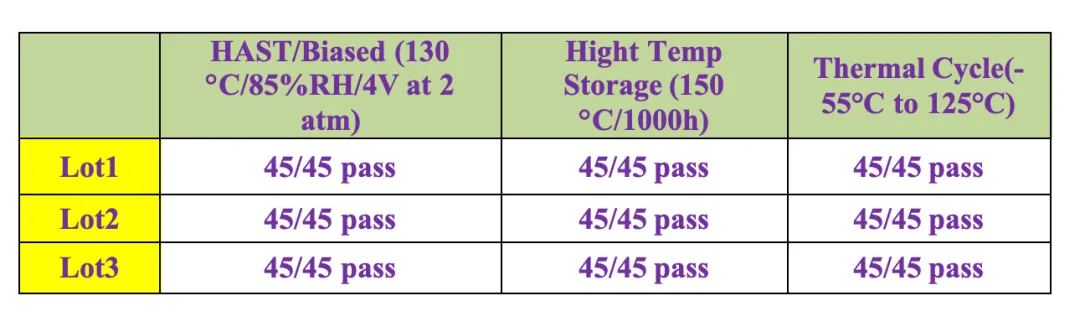

绝缘涂层键合线的可靠性和可行性研究在各种OEM进行了技术测试。引线键合在OEM中进行,使用标准生产的引线键合机(如:ASM Eagle、K&S、Iconx-Plus等),以及封装类型(如PBGA和引线框架)。

图11显示了可靠性数据的528根交叉总线,该器件使用K&S键合机制造。该器件中的芯片有上三层焊盘组成,焊盘间距为90μm(有效焊盘间距为30μm)。该器件有采用交叉键合形式形成线键合(图11所示),每个器件使用528根纯度为99.99%,直径为30μm的绝缘键合涂层线。

图片

图 11 : 503PBGA(40mm*40mm)是有528个交叉键合线形成,用于车规的测试芯片

“可靠性/ 评估内容 ”

1. JEDEC湿度等级3作为预调试( JESD-22-A113-B),并修改为无铅焊料;回流条件:在30C/60%RH,192小时。在245°C,焊料回流3次。

2. 温度循环(TC): (JESD-22- A104-A),条件B: -55℃至+125℃,电气测试点在500-1000个循环。

3. 150℃时的高温储存寿命(JESD-22-A103-A);500小时和1000小时的电气试验点

4. 偏置高加速应力试验(偏置高应力试验)(JeSD-22-A110-B)在2大气压下,温度为130℃/85%RH/4.0V,持续100小时。

图片

表 2 :绝缘涂层键合线在503 PBGA的可靠性实验总结

绝缘涂层键合金线

四/ 结论

绝缘涂层键合金线

为满足当前芯片行业高密度互连要求,绝缘涂层键合金线的方法,可实现复杂的封装设计,提高封装性能及产量。

绝缘涂层键合线的优势:

1. 防止电线短路

2. 超高密度芯片封装、超细、多行焊接和阵列键合

3. 多层芯片封装(如:DIE Stack \Sip以及Chip to Chip)

4. 当前制造应用(如:扫线、超长线弧、弯折线等)

5. 简化基板和缩小封装尺寸

本文提供了具有代表性的测试数据:

在绝缘涂层键合金线上的绝缘涂层键合技术:

1)第一和第二焊点的引线键合强度满足行业规范,是根据基于20μm、23μm和25μm金线的绝缘涂层键合金线实现的。绝缘涂层键合金线显示出良好的球形和对称性。

2)绝缘涂层键合金线的金属间化合物覆盖,在时间0时刻时与裸线相比,其覆盖率>75%的键合球面积。

3)用绝缘涂层键合线键合的车规级芯片,通过了JEDEC湿度等级3预调试(JESD-22-A113-B)后,交叉和接触的导线通过了可靠性测试(偏置HAST、HTS和TC)。

4) 绝缘涂层键合金线是环保的,并通过了EPATO17 规范。

4) 绝缘涂层键合金线即使在百万键合之后也不会使劈刀尖端余留残留物。

本文系转载,前往查看

如有侵权,请联系 cloudcommunity@tencent.com 删除。

本文系转载,前往查看

如有侵权,请联系 cloudcommunity@tencent.com 删除。

评论

登录后参与评论

推荐阅读