深入理解处理器的乱序执行与流水线-如何优化你的程序性能

一、处理器的流水线技术

流水线是一种处理器设计技术,利用并行性来提高处理器的性能。流水线技术将指令的执行过程分解为几个阶段,每个阶段可以并行处理多个指令。

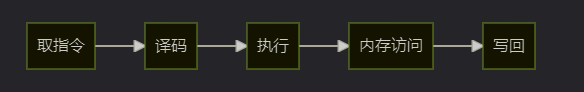

1.1 流水线的基本概念

在流水线设计中,处理器被分为几个阶段,每个阶段处理一部分任务。例如,一个简单的五级流水线可能包括取指令、译码、执行、内存访问和写回五个阶段。

1.2 流水线的优点和缺点

流水线的主要优点是提高了处理器的吞吐量,但同时也带来了一些问题,如管道冒险和分支预测等问题。

二、处理器的乱序执行技术

乱序执行是一种处理器设计技术,它允许处理器独立于程序顺序执行指令,以利用处理器资源并提高性能。

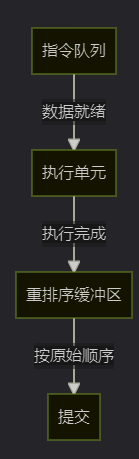

2.1 乱序执行的基本概念

乱序执行技术的主要目标是消除因数据依赖性导致的停顿。处理器将指令放入一个缓冲区,然后根据数据就绪的情况,选择任何可以执行的指令进行执行。

2.2 乱序执行的优点和缺点

乱序执行可以提高处理器的性能,但同时也带来了一些挑战,如需要复杂的硬件设计和指令调度算法。

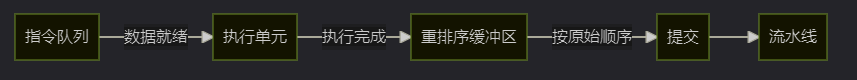

三、乱序执行与流水线的结合

通过将乱序执行和流水线技术结合起来,处理器可以有效地处理更多的指令并提高性能。例如,Intel的Core微架构就采用了这种技术。

四、实际应用示例

乱序执行和流水线技术在现代处理器设计中广泛应用,例如Intel的Core系列、AMD的Zen系列等。

在软件开发中,理解乱序执行和流水线技术也可以帮助我们更好地优化代码。例如,通过避免数据依赖性,我们可以提高代码的执行效率。

五、拓展阅读

如果你对处理器设计感兴趣,以下是一些推荐的拓展阅读:

- “Computer Organization and Design: The Hardware/Software Interface” by David A. Patterson and John L. Hennessy.

- “Modern Processor Design: Fundamentals of Superscalar Processors” by John Paul Shen and Mikko H. Lipasti.

本文参与 腾讯云自媒体同步曝光计划,分享自作者个人站点/博客。

原始发表:2024-12-23,如有侵权请联系 cloudcommunity@tencent.com 删除

评论

登录后参与评论

推荐阅读

目录