深入理解DRAM-3:DDR5

DDR5 是当前DRAM行业成熟工艺制程的最新产品,与DDR4 相比:

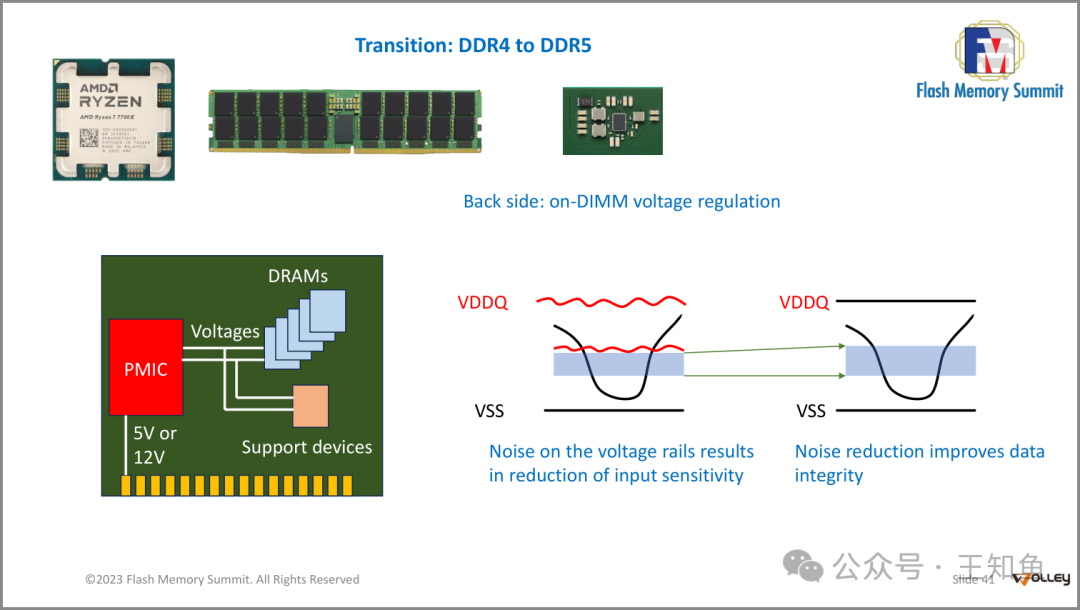

DDR5引入了DIMM上的电压调节(Back side: on-DIMM voltage regulation),以减少电源轨上的噪声(Noise reduction improves data integrity),从而提高输入灵敏度(Noise on the voltage rails results in reduction of input sensitivity)。图中还包含了一个内部电路图,显示了PMIC如何连接到电压轨上。

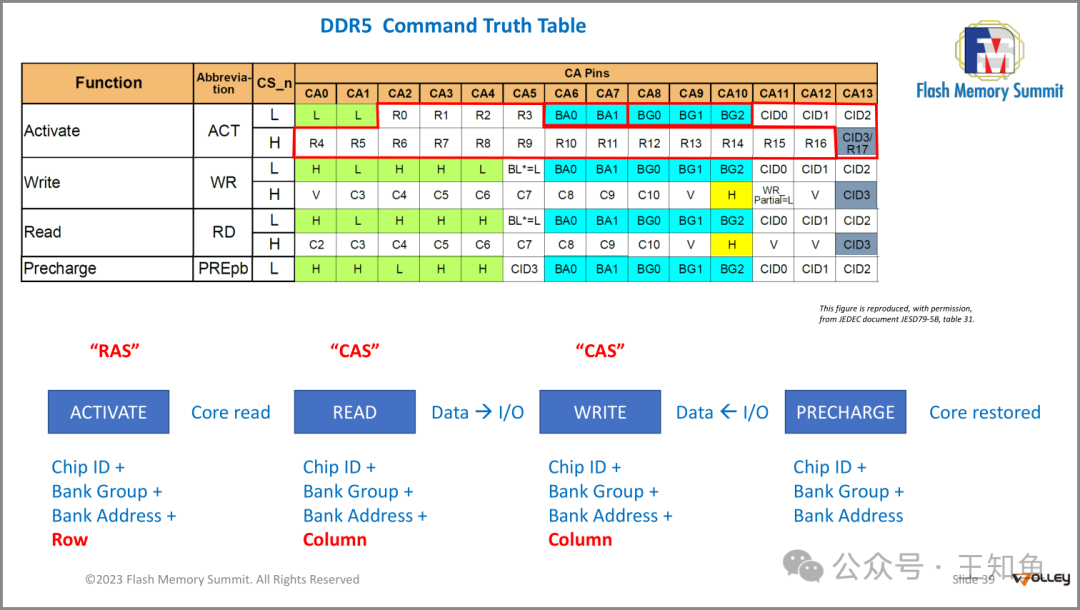

图示DDR5命令真值表(Command Truth Table),它详细说明了不同命令(Activate, Write, Read, Precharge)对应的引脚状态(CS_n, CA pins等)。

表格分为四部分,“RAS”、“CAS”、“CAS”和“CAS”,分别对应ACTIVATE、READ、WRITE和PRECHARGE四个动作及其所需的信号组合。例如,激活(ACTIVATE)需要Chip ID、Bank Group、Bank Address和Row信息;读取(READ)需要Chip ID、Bank Group、Bank Address和Column信息;写入(WRITE)也需要同样的信息;最后,预充电(PRECHARGE)只需要Chip ID、Bank Group和Bank Address信息。

表格对于理解DDR5内存的工作原理非常有帮助,因为它描述了控制器如何通过特定的引脚状态向内存模块发送各种命令。

内存控制器(Memory Controller)和命令真值表有什么关系呢?

内存控制器(Memory Controller)是负责管理与内存交互的硬件组件,它位于CPU或北桥芯片中,在现代系统中通常集成在CPU内部。内存控制器的任务包括但不限于接收来自CPU的数据读写请求,将这些请求转换为适合内存模块的操作命令,管理内存寻址,控制内存的刷新周期,以及处理数据的传输。

内存控制器与命令真值表之间的关系体现在以下几个方面:

- 1. 命令生成:当CPU发出读写请求时,内存控制器根据请求的类型生成相应的内存命令。这些命令需要按照命令真值表的规定,设置正确的控制引脚状态,以确保正确的命令被发送到内存模块。

- 2. 时序控制:内存控制器还必须遵守命令真值表中规定的时序要求,例如,在发送读或写命令之前,可能需要先发送激活(Activate)命令打开正确的行,然后在适当的时间间隔后发送读或写命令。内存控制器需要确保这些命令按正确的顺序和时间间隔发送。

- 3. 错误检测与纠正:内存控制器还可能包含错误检测和纠正机制,这在一定程度上依赖于命令真值表来确定哪些命令序列是合法的,哪些可能是错误的。

- 4. 刷新管理:命令真值表也会列出刷新(Refresh)命令的触发条件,内存控制器需要定期执行刷新操作,以维持动态RAM中的数据不丢失。

简而言之,内存控制器基于命令真值表来正确地生成和发送内存命令,以保证内存的正常读写操作和其他功能的正确执行,可以把真值表理解成计算体系的指令集,而MC则是负责翻译和执行指令集的计算单元。

DDR5 新增功能

伴随系统通信信号的底层优化,最新一代DDR5在功能上通过软硬结合定义出多种新特性,以下逐一介绍。

Error Check Scrub (ECS)

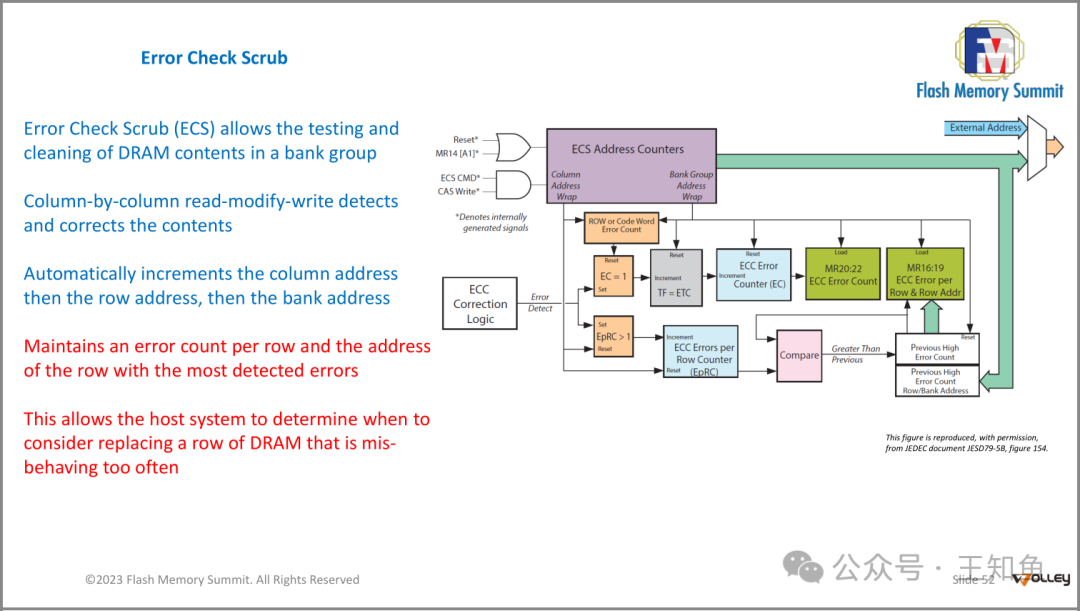

Error Check Scrub (ECS),允许测试和清理Bank组中DRAM内容。通过列读修改写操作检测和纠正内容,并自动递增列地址,然后行地址,再然后Bank地址。此外,它还会维护每行的错误计数和错误最多的行的地址,以便主机系统可以决定何时替换行为异常的DRAM行。

Error Check Scrub (ECS)主要用于以下场景:

- 1. 故障排除和诊断:当系统遇到内存相关的问题时,ECS可以帮助定位问题的具体位置,比如哪一行DRAM出现了过多的错误。这对于故障排除和诊断非常重要,因为它能提供有关内存健康状况的详细信息。

- 2. 长期稳定性监控:在服务器和数据中心环境中,ECS可用于监控内存的长期稳定性。如果某一行DRAM频繁出错,那么系统可以根据ECS提供的信息决定是否需要更换该行,以避免潜在的数据损坏或系统崩溃。

- 3. 内存校验:在某些安全关键的应用程序中,ECS可以作为额外的安全层,确保内存内容的准确性。例如,在金融交易或医疗设备中,任何内存错误都可能导致严重后果,因此这种自我检查和修复功能至关重要。

- 4. 实验研究:研究人员可能会使用ECS来分析内存错误模式,了解其原因,或者评估不同内存配置下的错误率。

- 5. 内存测试:在生产过程中,制造商可以使用ECS来测试新生产的内存模块的质量,确保其符合规格。

- 6. 老化管理:随着内存使用时间的增长,一些位可能会逐渐变得不稳定。ECS有助于发现这些问题并在它们导致严重问题之前采取措施。

- 7. 故障预防:在高可用性系统中,ECS可以帮助预防因内存错误而导致的服务中断,通过提前识别和替换有问题的内存行。

Memory Built In Self Test (MBIST)

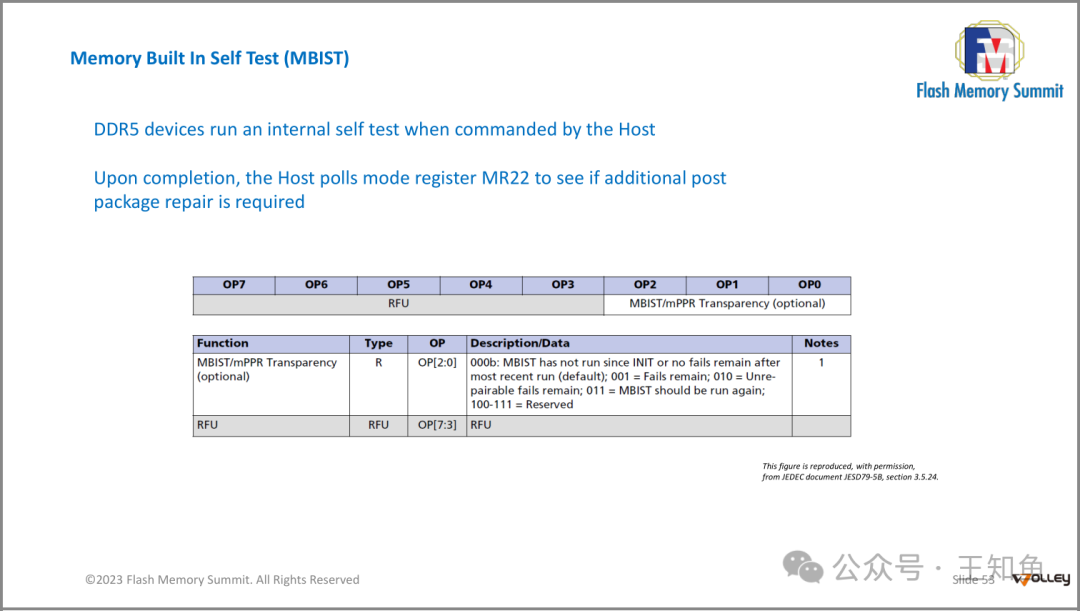

Memory Built-In Self Test (MBIST) 是一种内置自测技术,它允许DDR5设备在接收到主机指令时进行内部自检。以下是MBIST的工作原理:

- 1. 启动测试:当主机命令DDR5设备运行MBIST时,设备开始执行一系列预先编程的测试。

- 2. 测试过程:MBIST会生成并注入特定的测试模式到内存阵列,然后读回结果并与预期的结果进行比较。如果有任何差异,则表示可能存在错误。

- 3. 报告结果:完成测试后,设备将结果存储在一个称为模式寄存器(Mode Register,MR)的位置,通常是MR22。主机可以通过查询这个寄存器来获取测试结果。

- 4. 决策制定:如果测试结果显示存在未修复的错误,主机可以决定是否需要进一步的修复步骤,如Post Package Repair (PPR)。

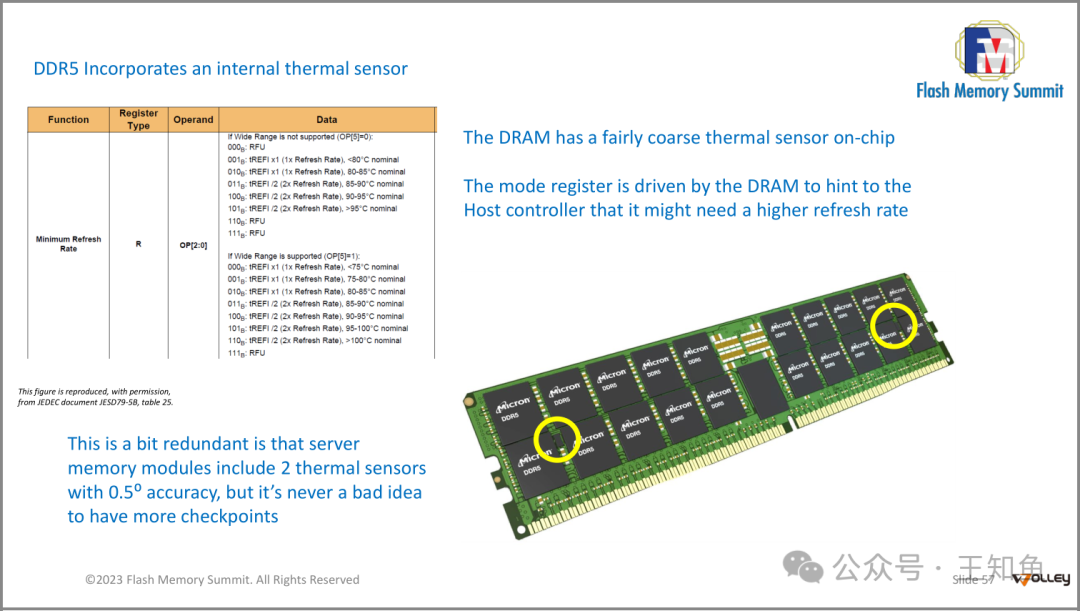

Internal Thermal Sensor

DDR5内存模块具有一个内置的热传感器,该传感器能够感知温度并将其反馈给主控。

当温度超过一定阈值时,如温度在85℃以下,保持单次刷新频率,超过则2倍刷新频率(Wide Range 功能支持更细粒度的温度控制),内存模块会向主控提示需要增加刷新速率以保持数据的稳定性。虽然服务器内存模块通常已经包含了两个精度为0.5度的热传感器,但多一层保障总是好的。

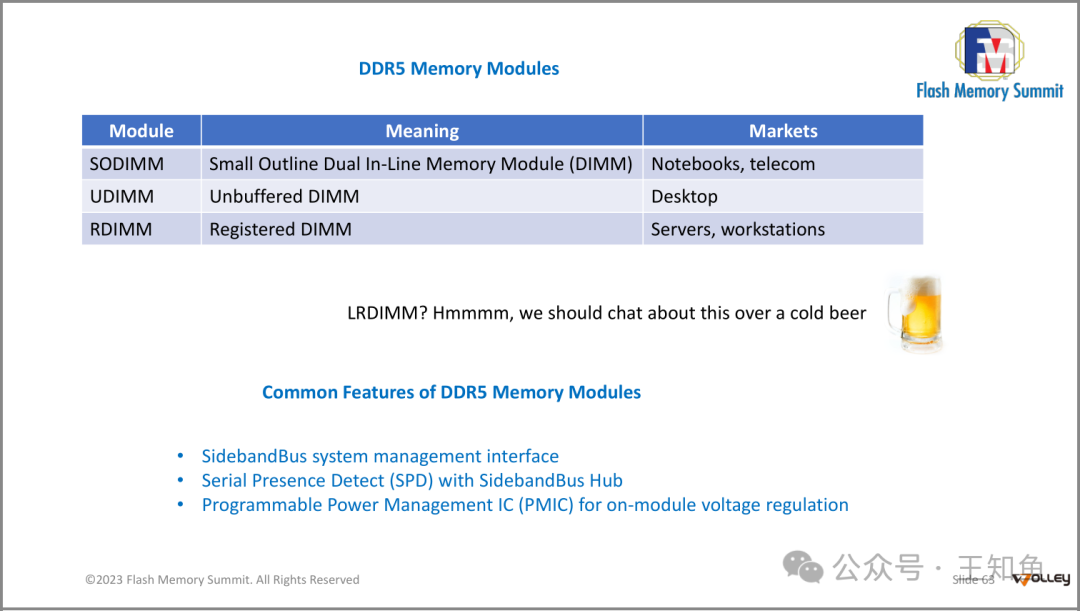

DDR5 模组

DDR5内存模块的不同类型对应不同市场,包括:

- • SODIMM:Small Outline Dual In-Line Memory Module,用于笔记本电脑和电信领域;

- • UDIMM:Unbuffered DIMM,用于台式机;

- • RDIMM:Registered DIMM,用于服务器和工作站。

DDR5内存模块的共同特征,包括:

- • SidebandBus系统管理接口;

- • Serial Presence Detect (SPD) with SidebandBus Hub;

- • Programmable Power Management IC (PMIC) for on-module voltage regulation。

这些特性使得DDR5内存模块更加高效、可管理并且具备更好的电源管理能力。

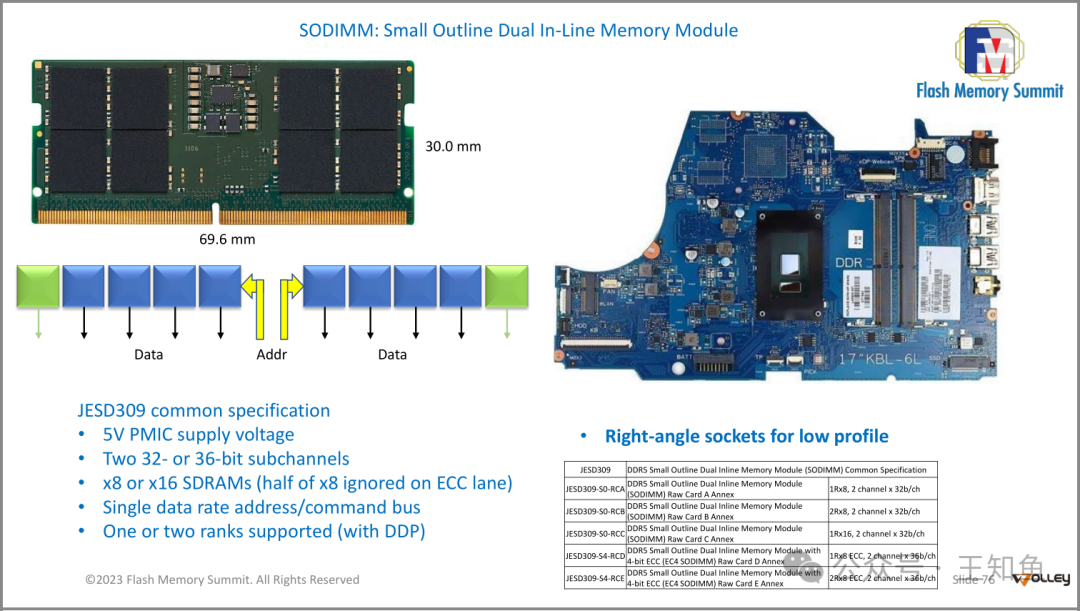

SODIMM-小型双列直插内存模块

SODIMM的一般特性:

- • JESD309通用规范

- • 5V PMIC供电电压

- • 两个32或36位子通道

- • x8或x16 SDRAMs(ECC x8被忽略)

- • 单一的数据/命令总线速度

- • 支持一或两行(使用DDP)

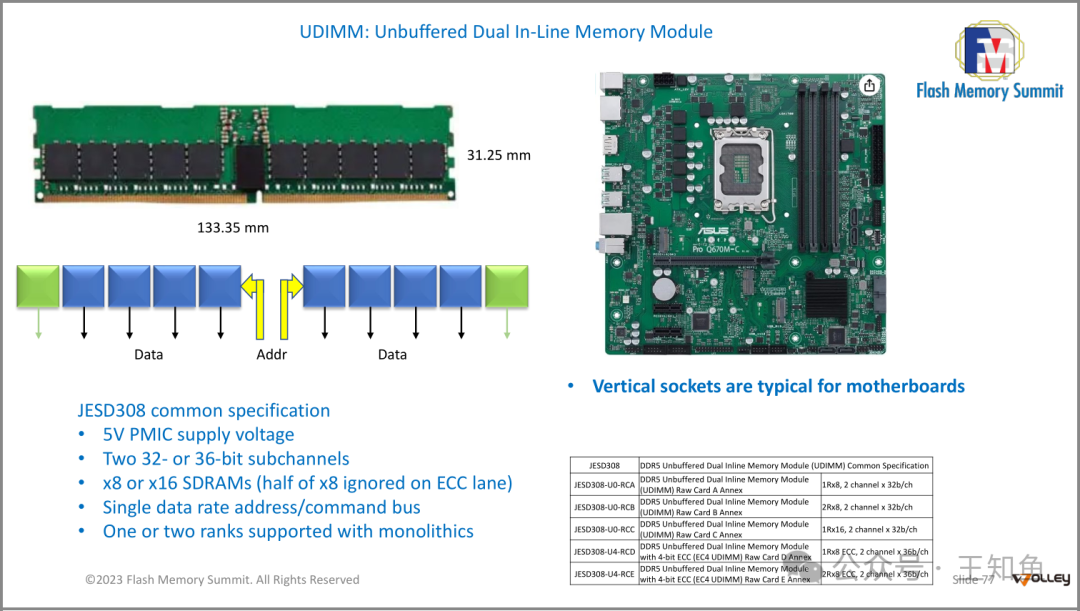

UDIMM

与SODIMM基本保持一致。

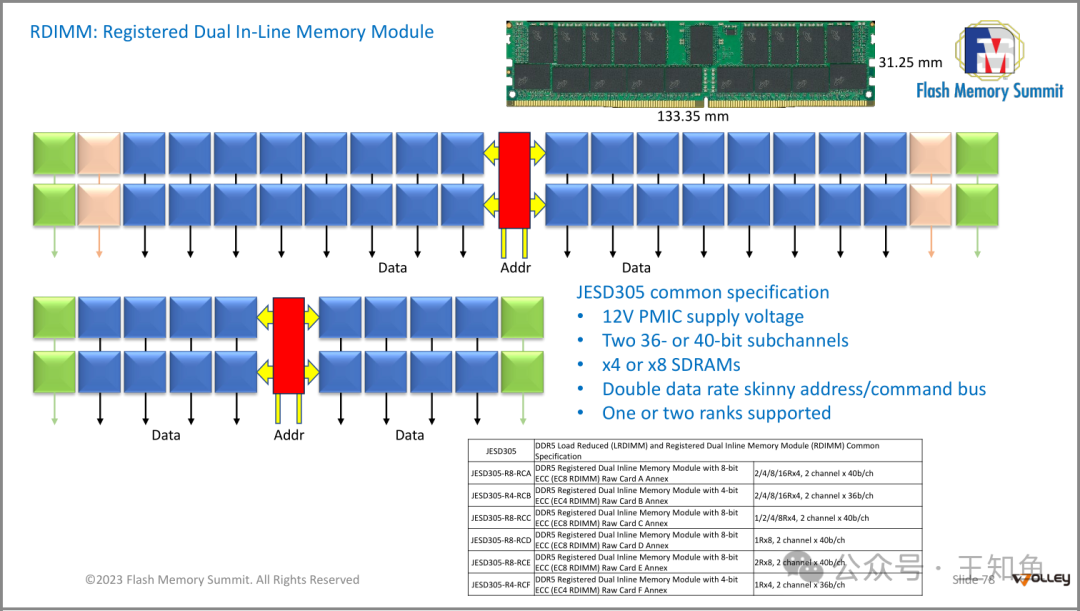

RDIMM-双列直插内存模块

应用于工作站和服务器的DIMM外观与应用于台式机的UDIMM 大致相同,主要差异点在:

- 1. 工作电压从5V升级到12V;

- 2. 基于ECC机制,位宽较前两者要高一点;

- 3. 接口宽度较SODIMM 和 UDIMM 的宽度下降,保留 x4 和 x8(为什么会下降?大概率还是服务器场景的功耗考虑)

- 4. 支持双路寻址

小结

DDR5关键技术特性

电压调节与噪声抑制:DDR5引入了DIMM上的电压调节技术,有效降低电源轨噪声,提升数据完整性及输入灵敏度。

DDR5新增功能

- 1. Error Check Scrub (ECS) :允许自动检测和纠正DRAM内容错误,维护错误计数,增强数据可靠性。

- 2. Memory Built-In Self Test (MBIST) :内置自测技术,实现DDR5设备的内部自检,提升故障排查与诊断效率。

- 3. Internal Thermal Sensor:内置热传感器监测温度,动态调整刷新频率,确保数据稳定性和延长内存寿命。

DDR5模组类型及特性

- 1. SODIMM:适用于笔记本电脑和电信领域,具备SidebandBus系统管理接口及电源管理IC。

- 2. UDIMM:用于台式机,特性与SODIMM相似。

- 3. RDIMM:针对服务器和工作站设计,支持更高电压和ECC机制,具备双路寻址能力,优化功耗管理。

以上特性共同推动了DDR5在性能、可靠性和能效方面的显著提升。

本文参与 腾讯云自媒体同步曝光计划,分享自微信公众号。

原始发表:2024-08-13,如有侵权请联系 cloudcommunity@tencent.com 删除

评论

登录后参与评论

推荐阅读

目录