一文精通STM32时钟树-以F401为例

主要就是主要和次级

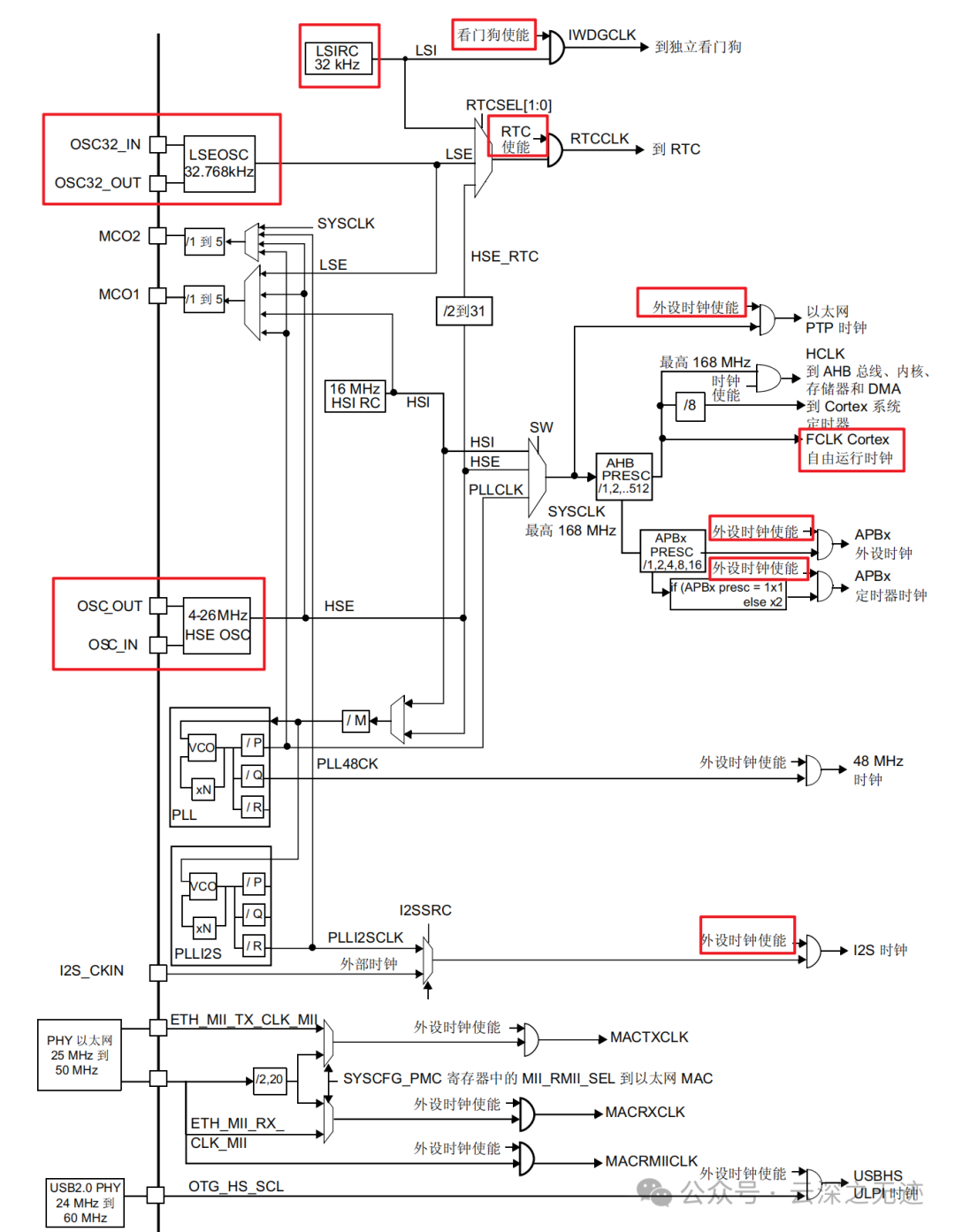

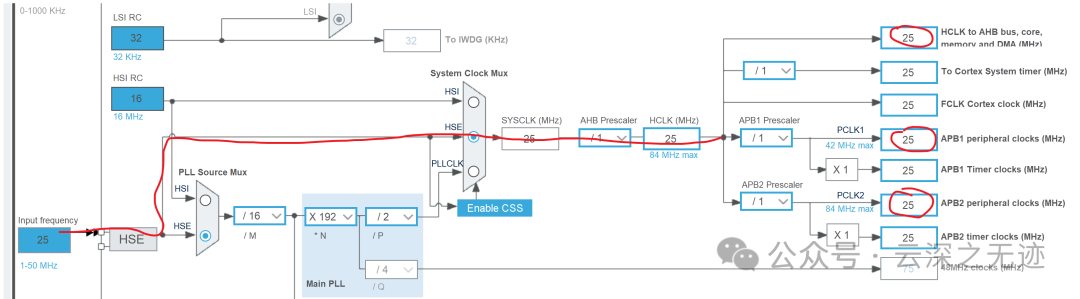

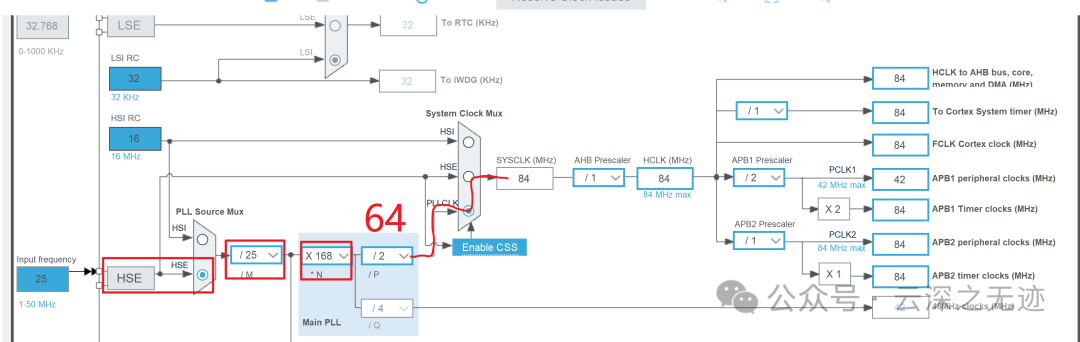

关键就是这个时钟树了

首先就是所有的时钟都有使能功能。

也有一些默认的时钟分频

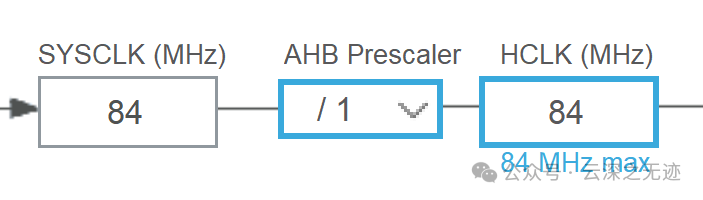

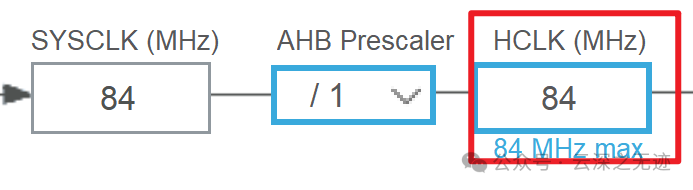

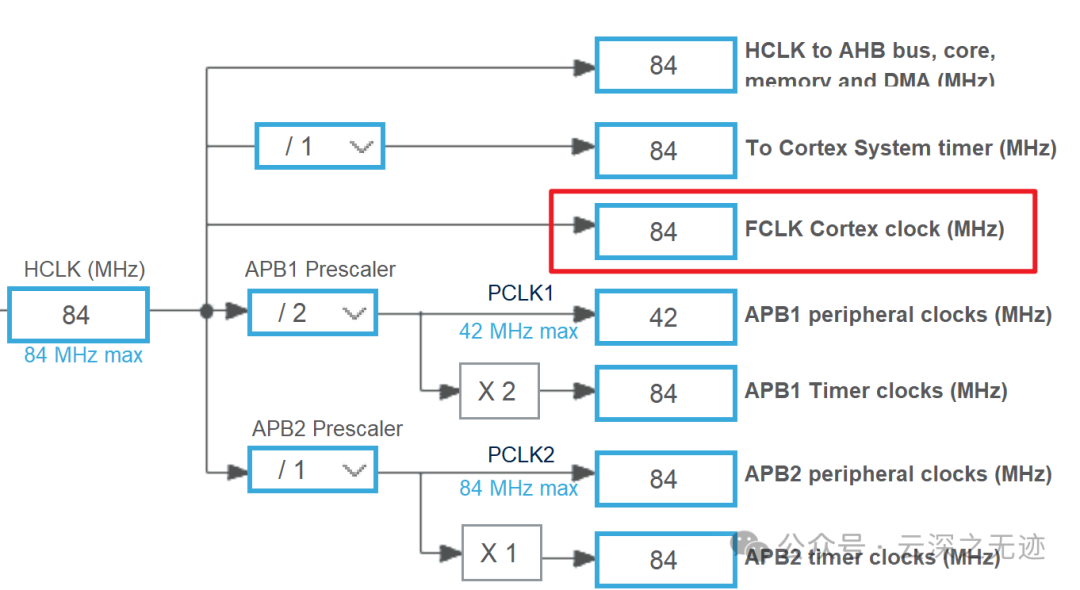

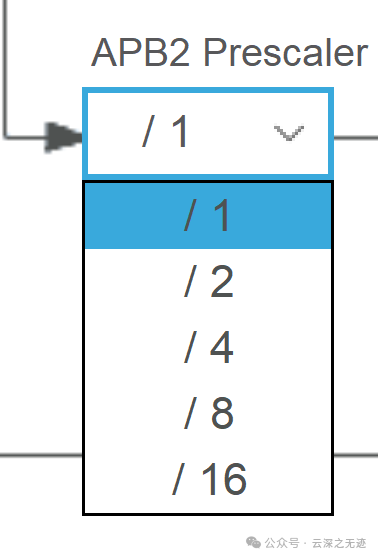

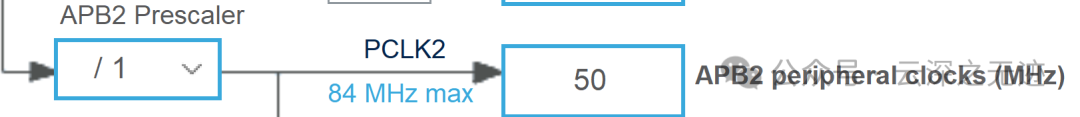

可通过多个预分频器配置 AHB 频率、高速 APB (APB2) 和低速 APB (APB1)。

AHB 域的最大频率为 168 MHz。

高速 APB2 域的最大允许频率为 84 MHz。

低速 APB1 域的最大允许频率为 42 MHz。

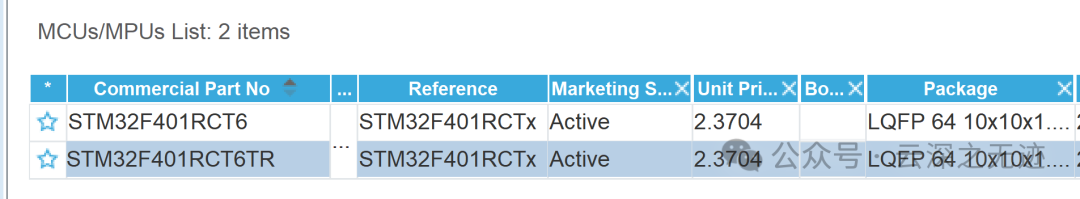

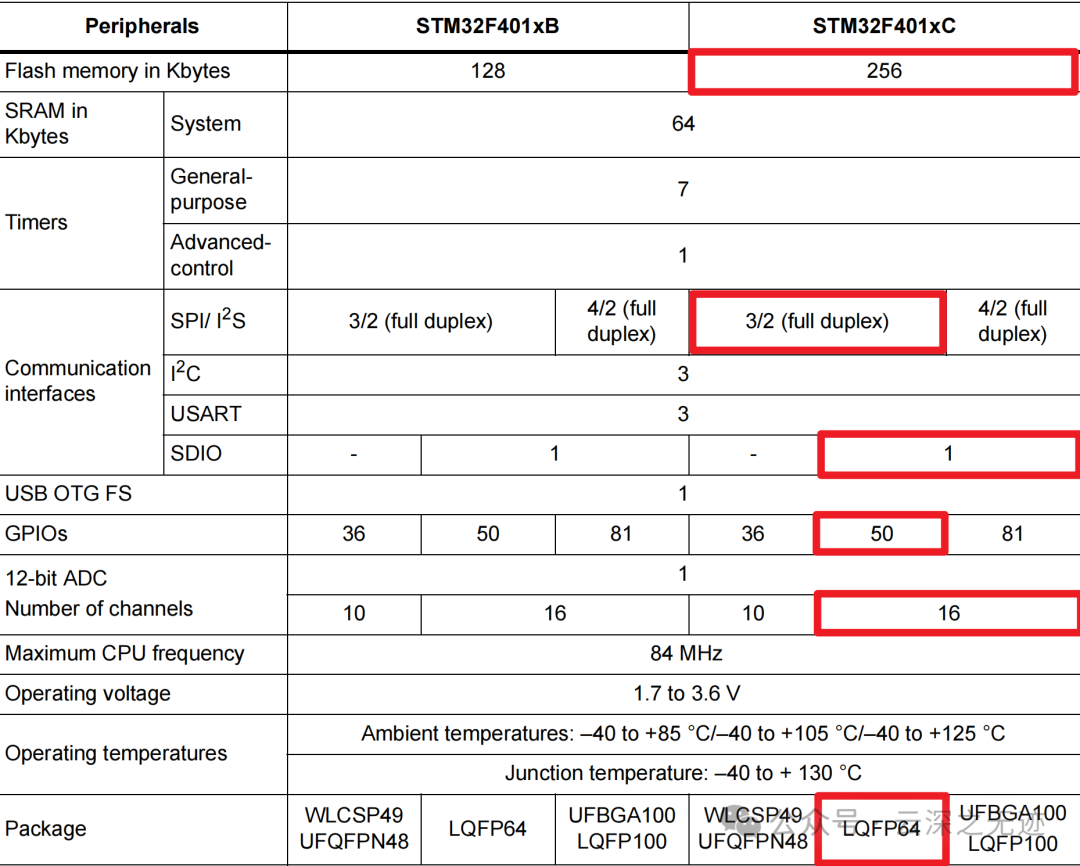

TR为带料,每次选的时候都迷惑

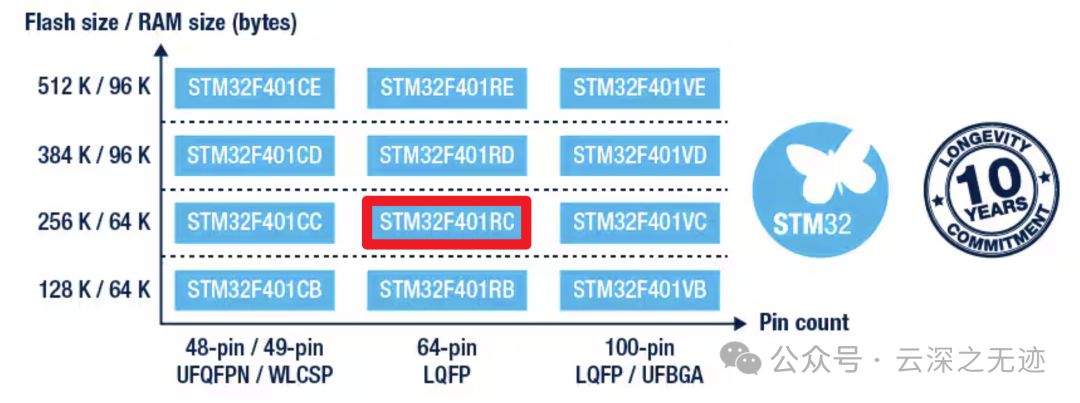

是一个中间的型号

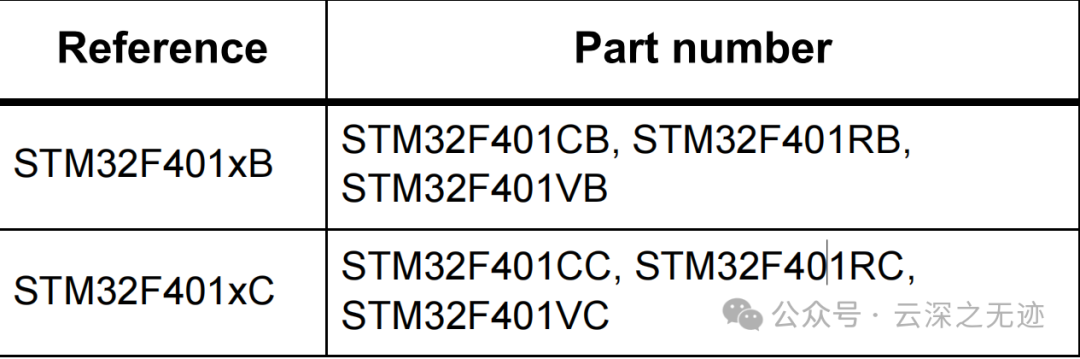

涵盖这俩类子型号

参考手册

是256KB的大内存版本

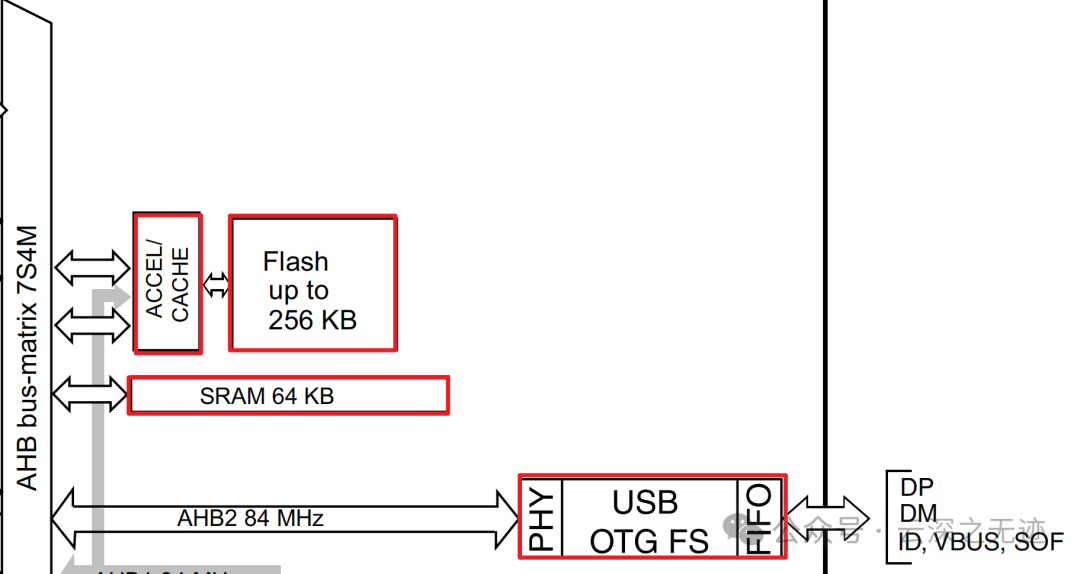

可以看到都整合到了总线上面

I-Code:此总线用于将 CPU 内核的指令总线连接到 Flash 指令接口。通过此总线可执行预取操作。

D-Code:此总线用于将 CPU 的 D-Code 总线(数据加载和调试访问)连接到 Flash 数据接口。

S总线用于将 Cortex™-M4F 数据总线和 64 KB CCM 数据 RAM 连接到总线矩阵。内核通过此总线进行立即数加载和调试访问。此总线访问的对象是包含代码或数据的存储器(内部Flash 或通过 FSMC 的外部存器)。

通过一个AHB连接所有外设

flash慢,这里还使用了一个缓存器。内存高达64KB,USB可以看到是一个直接的外设。

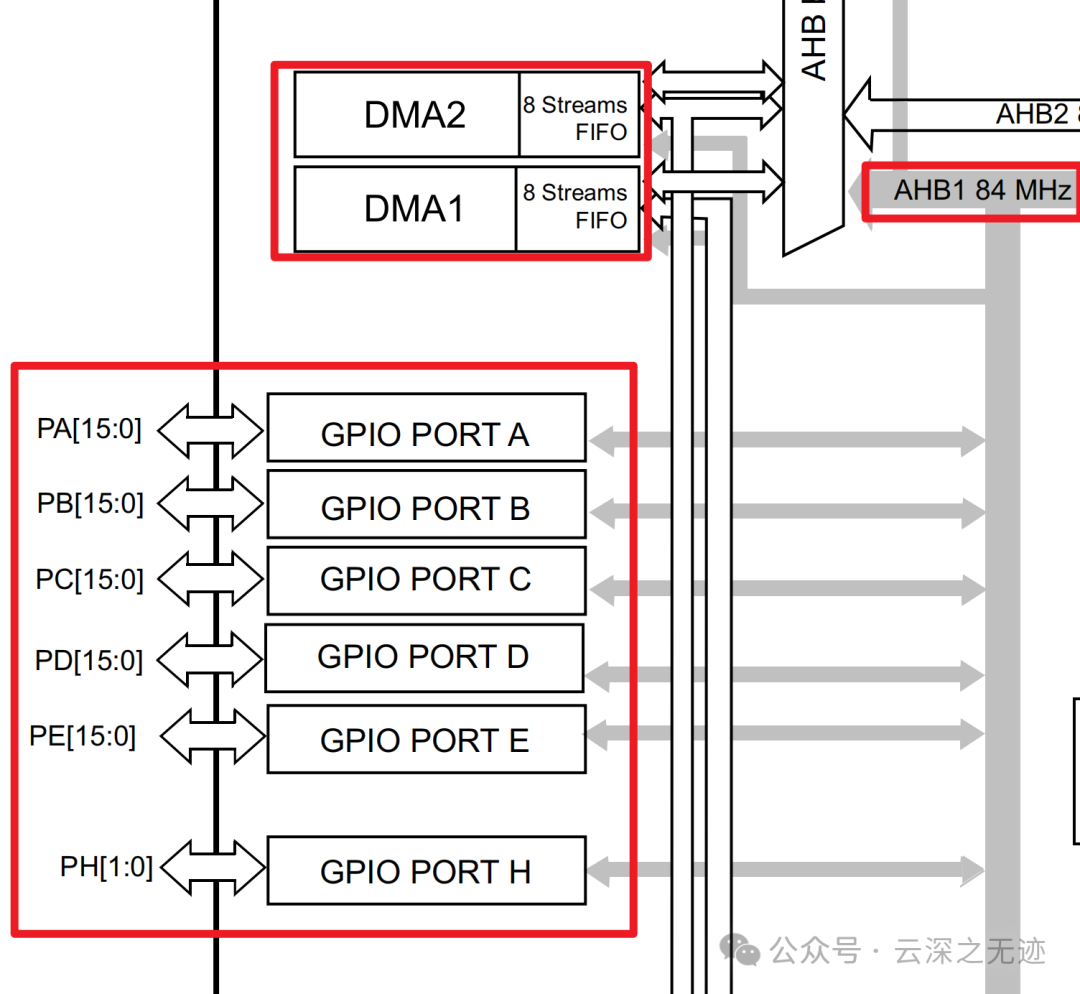

有两个DMA

GPIO都在AHB1上面,速度最大84Mhz,就在高性能的主干线上面。DMA也是。

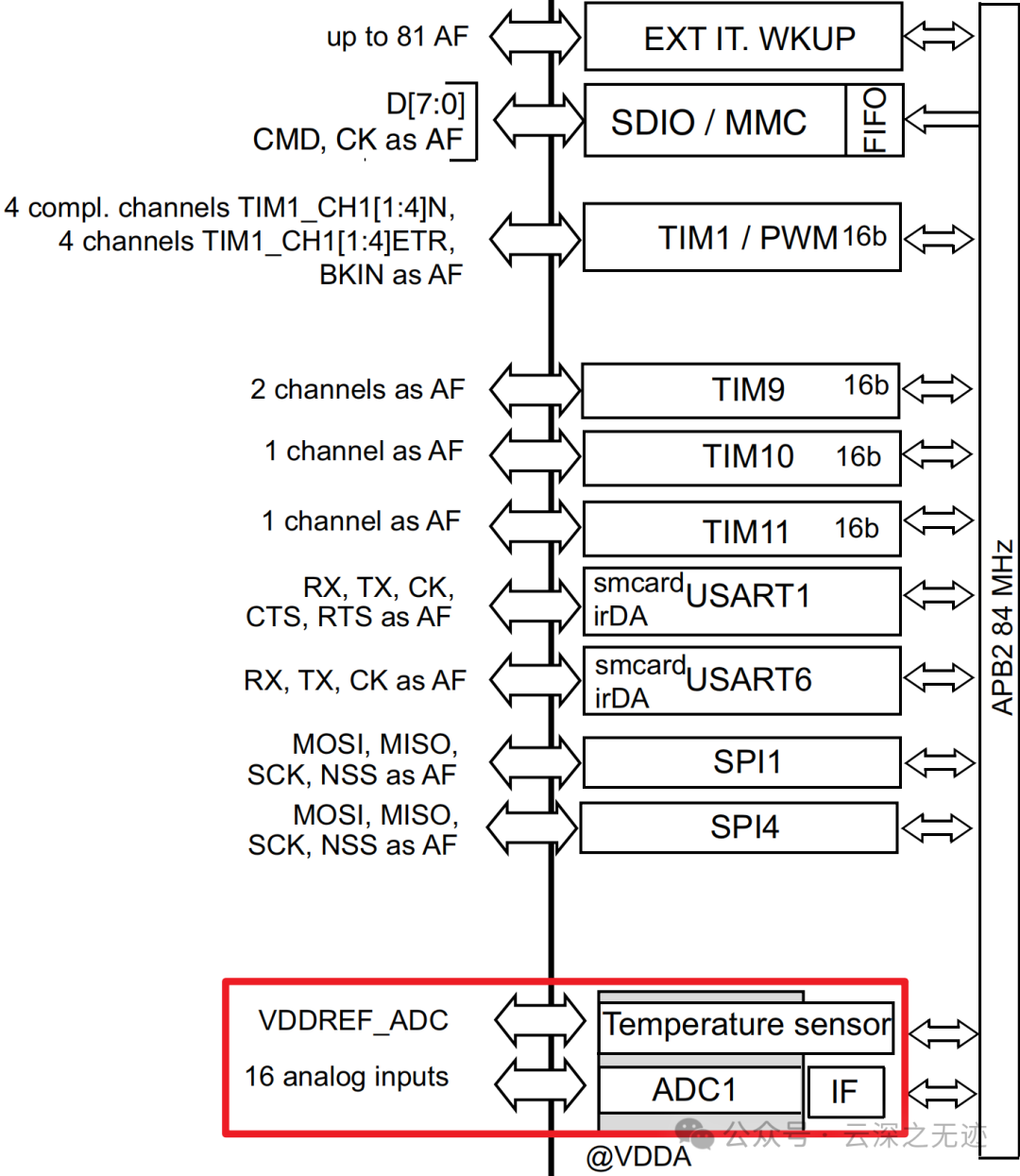

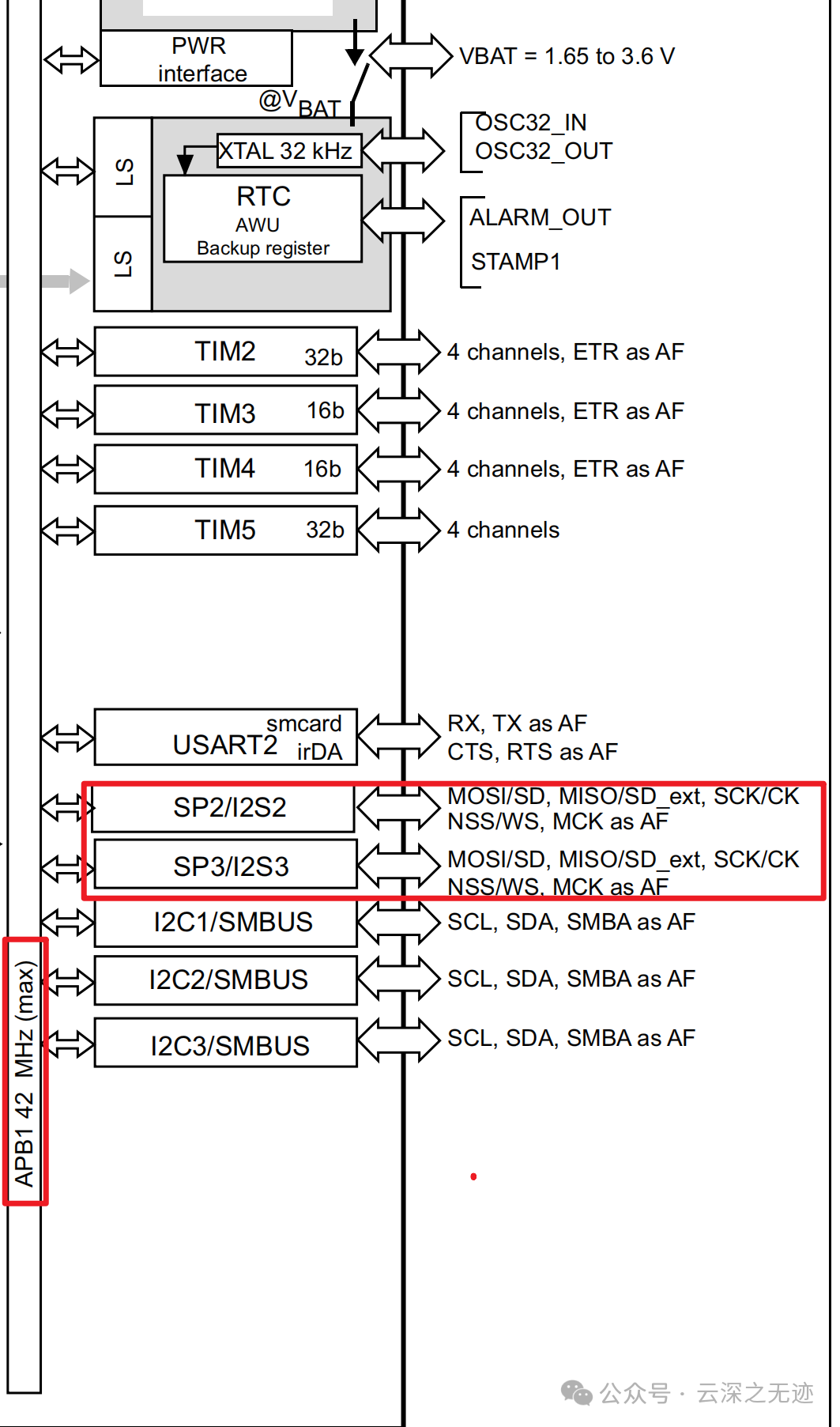

APB1和2都在角落里面,右下角

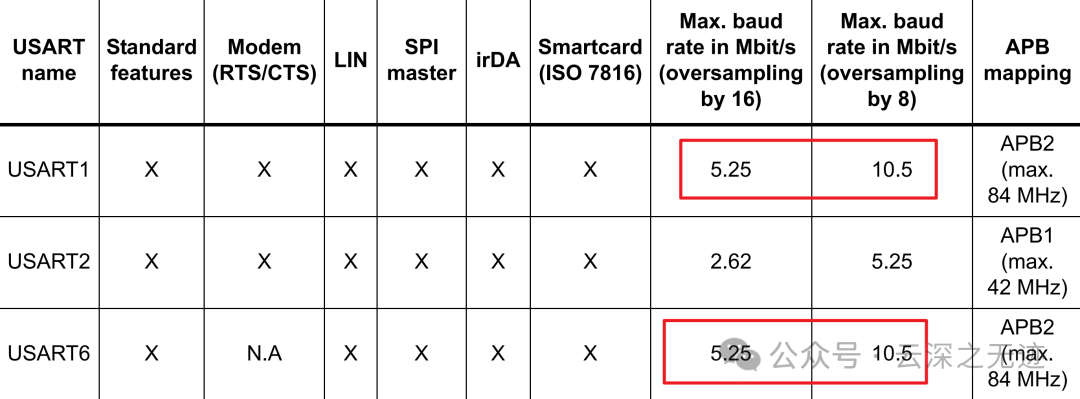

APB1上面连接的是低速外设,包括电源接口、备份接口、CAN、USB、I2C1、I2C2、USART2、USART3等。

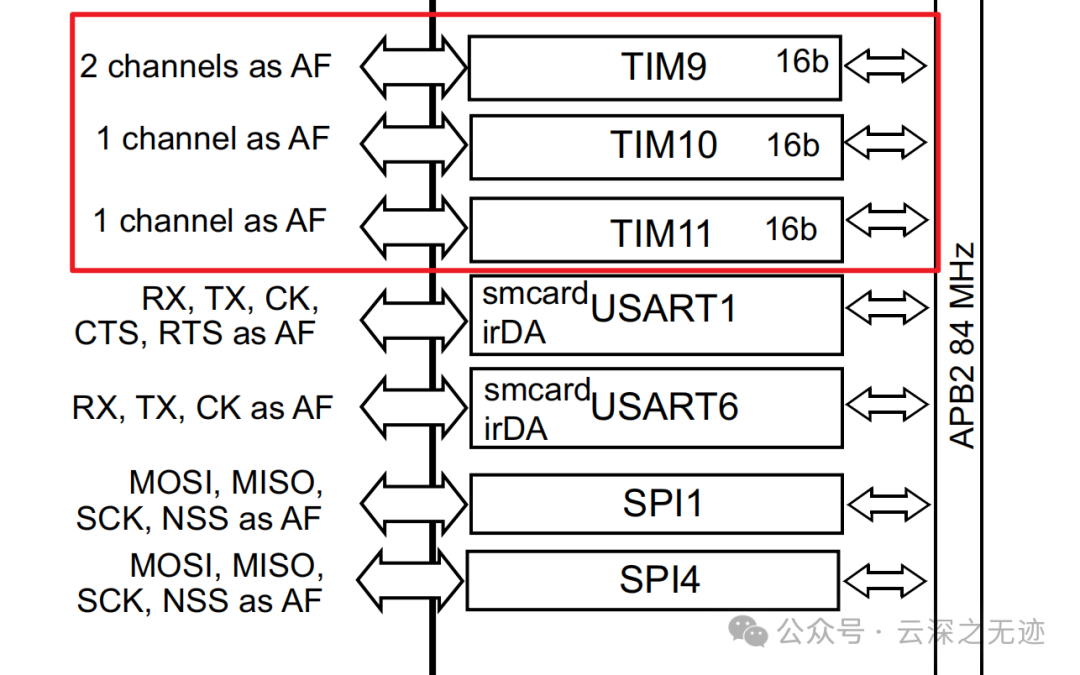

APB2上面连接的是高速外设包括USART1、SPI1、Timer1、ADC1、ADC2、GPIO等。

APB2也可以到84M

看样子,是AHB转到了APB的

右边是APB1的外设线,可以到42M

在使用外设的时候一定看时钟

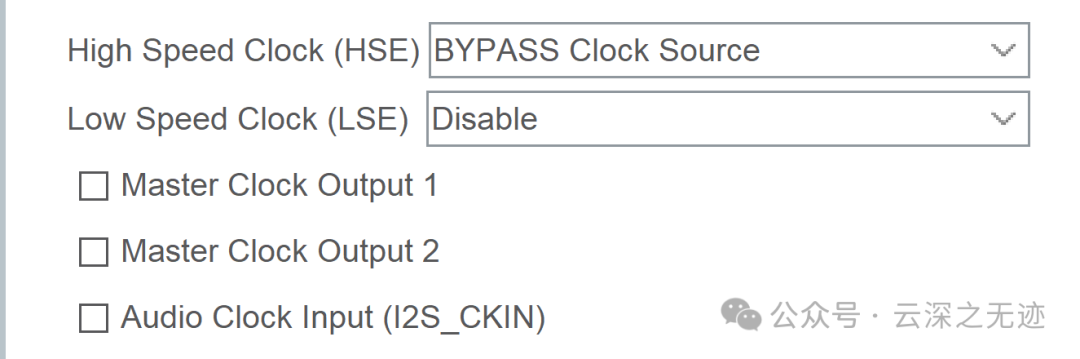

一般我们有自己的晶振

第二种

需要在这里开启外部晶振

就是这样的一条线

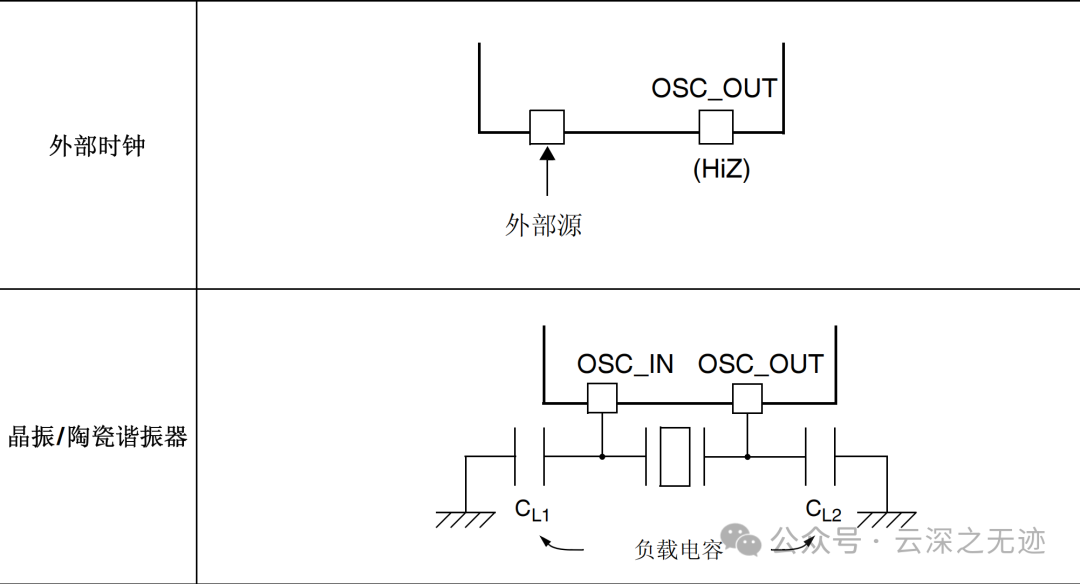

HSE(High Speed External):高速外部时钟源,通常为晶振。HSE也是STM32芯片的默认时钟源之一,其频率范围可以在1MHz到25MHz之间。HSE可以作为系统时钟和PLL锁相环输入,还可以经过128分频后输入给RTC。

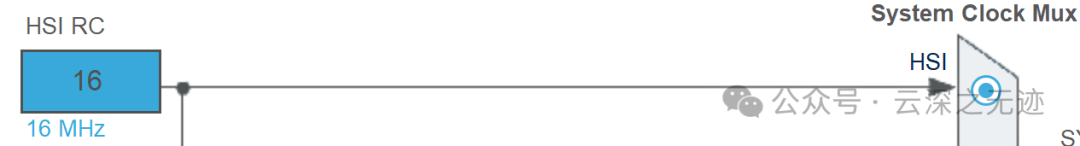

靠上一点是HSI

高速内部时钟源(Internal),时钟频率为8MHz。HSI是STM32芯片默认的时钟源之一,因为其时钟稳定性和精度较高。可作为系统时钟或PLL锁相环的输入。

HSI 时钟信号由内部 16 MHz RC 振荡器生成,可直接用作系统时钟,或者用作 PLL 输入。

HSI RC 振荡器的优点是成本较低(无需使用外部组件)。此外,其启动速度也要比HSE晶振快,但即使校准后,其精度也不及外部晶振或陶瓷谐振器。

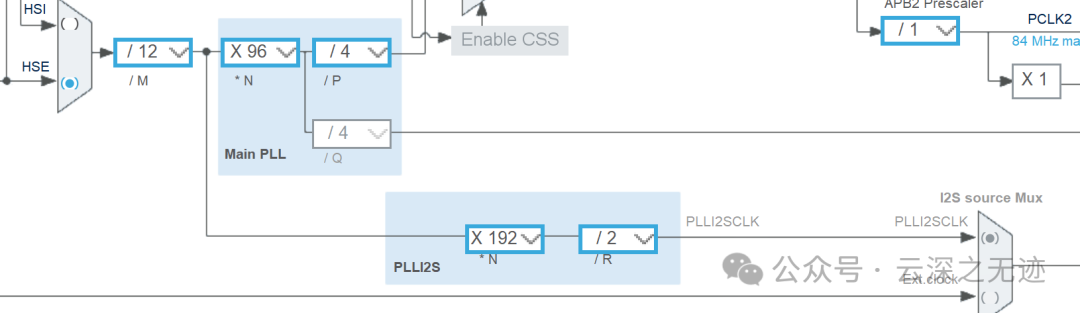

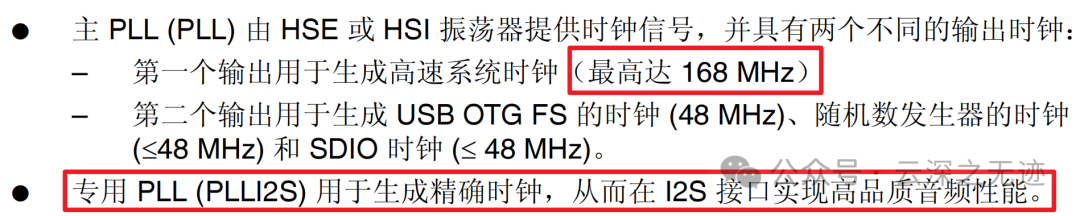

两个PLL

作用在此,PLL就是可以让系统工作到最大频率

我发现-PLL:锁相环倍频输出 可以让后面的时钟跑满

其时钟输入源可选择为HSI/2、HSE或者HSE/2。倍频可选择为2~16倍,但是其输出频率最大不得超过72MHz。

时钟环路是这样的

锁相环的作用包括:

- 时钟信号重构:锁相环可以将不稳定的输入时钟信号转换为稳定的输出时钟信号,以提高系统时钟的精度和稳定性。

- 时钟信号分频:锁相环可以将高频率的时钟信号按照一定比例分频,以适应不同的系统时钟需求。

- 时钟信号倍频:锁相环可以将低频率的时钟信号按照一定比例倍频,以适应高速系统时钟的需求。

- 频率合成:锁相环可以将不同频率的输入信号合成为一种新的频率信号,以适应某些特定的应用,例如无线通信。

- 相位检测:锁相环可以检测输入信号的相位差异,并将其与参考信号的相位进行比较,以实现相位同步。

SYSCLK是指系统时钟,是指计算机系统的主时钟信号,也是整个系统的主时钟。SYSCLK信号的频率决定了整个系统的运行速度和性能。

在微处理器系统中,SYSCLK信号通常由晶体振荡器或其他外部时钟源提供,然后经过分频、倍频等处理后,作为CPU、内存、外设等各个部分的时钟信号。SYSCLK信号的频率越高,系统运行速度越快,但同时也会增加功耗和热量等问题。

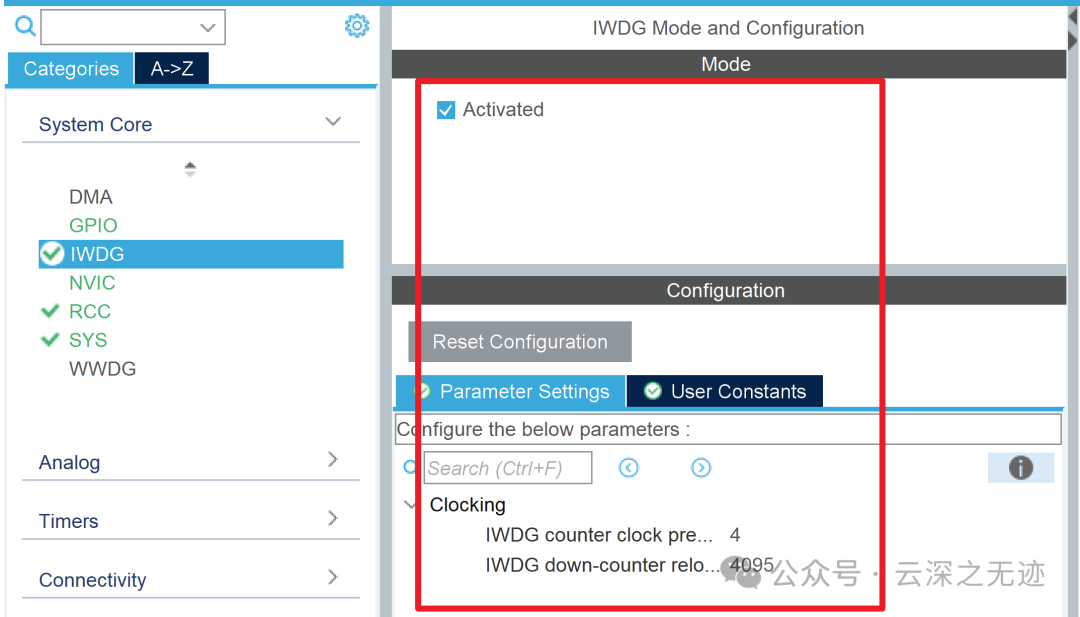

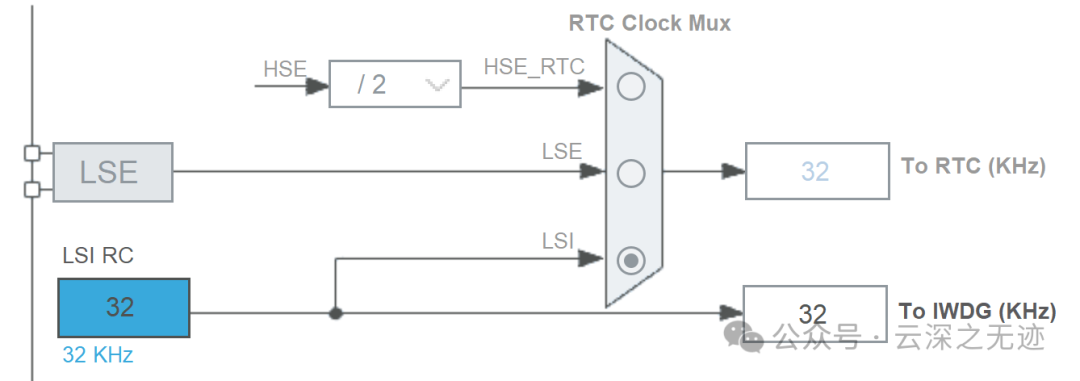

RTC和IWDG是独立的时钟系统

LSE 晶振是 32.768 kHz 低速外部 (LSE) 晶振或陶瓷谐振器,可作为实时时钟外设 (RTC) 的时钟源来提供时钟/日历或其它定时功能,具有功耗低且精度高的优点。

RTC时钟是指实时时钟(Real-Time Clock),是计算机系统中一种独立于CPU的时钟源,用于提供系统的实时时钟功能。与SYSCLK不同,RTC时钟一般不受系统运行状态的影响,即使系统处于关机状态,RTC时钟也可以继续运行。

RTC时钟通常由一个独立的晶体振荡器提供,其频率通常为32.768kHz。RTC时钟的精度和稳定性很高,可以保证系统的时间精度和稳定性。

呦西

看门狗时钟是一种硬件定时器,它在计算机系统中用于监控系统的运行状态,当系统出现异常或死锁等情况时,看门狗时钟可以重启系统以恢复正常运行。看门狗时钟通常由一个独立的计数器和一个独立的晶体振荡器组成,其工作原理类似于定时器。

要使能

可以看到激活了

直接从HCLK出去的

Systick是一种硬件定时器,是ARM Cortex-M系列芯片中的一种系统时钟,它提供了一个简单的计时器,用于计算器芯片的时间。所以可以说Systick属于时钟的一种。

Systick计时器由计数器和中断控制器组成,它的计数器可以在芯片上电后自动开始计数,时间间隔由寄存器SYST_RVR来设置,一般设置为1ms。当计数器达到设定值时,Systick计时器就会触发一个中断,通过中断处理函数可以实现各种定时任务。

这里

HCLK为高性能总线AHB(advanced high-performance bus)提供时钟信号。由系统时钟SYSCLK分频得到,一般不分频时等于系统时钟,是给外设使用的。

还有一个FCLK

FCLK(free running clock)是自由运行时钟,为CPU内核提供时钟信号。我们所说的CPU主频为xxHz,指的就是这个时钟信号频率,CPU时钟周期就是1/FCLK。

“自由”表现在它不来自系统时钟HCLK,在系统时钟停止时FCLK也继续运行。FCLK用作采样中断或者为调试模块计时。在处理器休眠时,通过FCLK可以采样到中断和跟踪休眠事件。Cortex-M3内核的FCLK和HCLK互相同步、互相平衡,保证Cortex-M3的延迟相同。

我个人感觉是可以通过观测FCLK来推测HCLK。

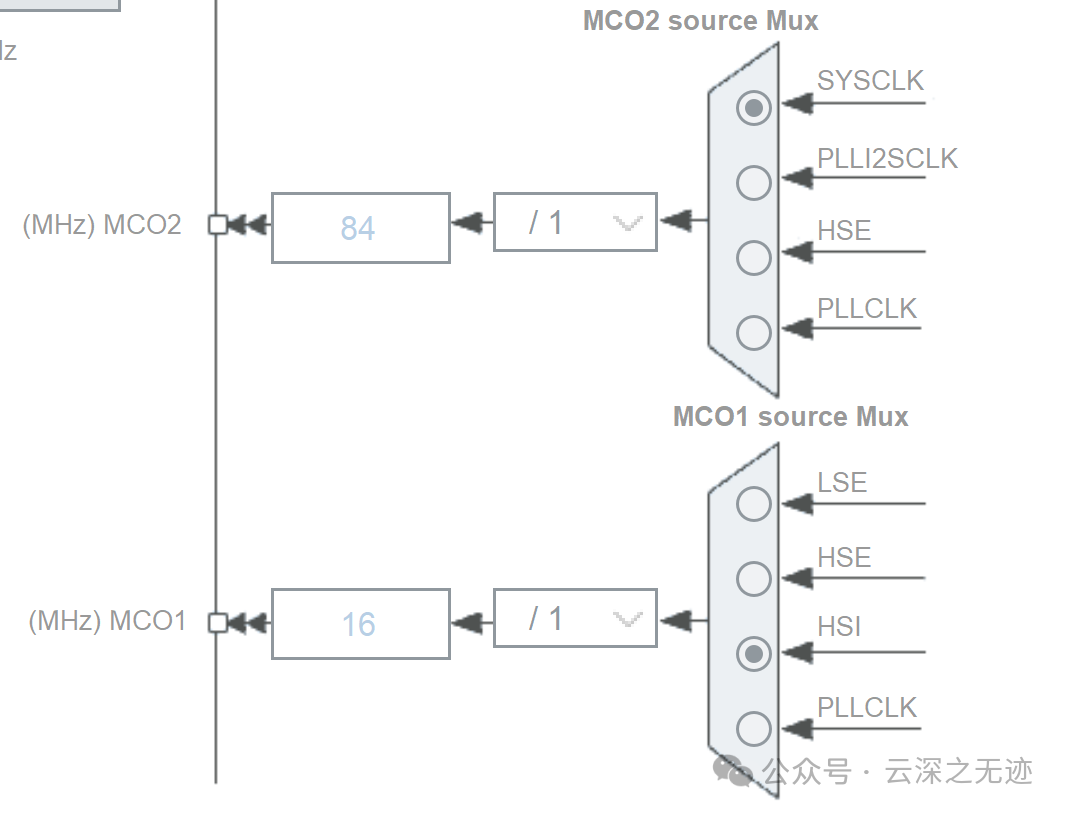

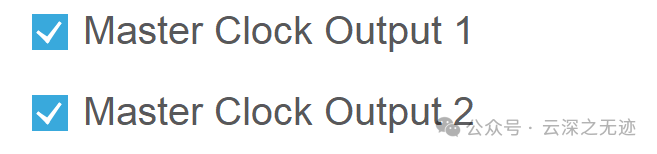

这个时钟也可以输出

MCO是STM32系列芯片中的一个时钟输出引脚,全称为Master Clock Output。MCO引脚可以将芯片内部的时钟信号输出到外部,用于连接到其他芯片或模块中,例如外部时钟源、LCD显示器等。

MCO引脚可以输出多种类型的时钟信号,包括系统时钟、PLL时钟、HSE时钟等。输出的时钟信号频率和类型可以通过寄存器设置来控制,以满足不同的应用需求。同时,MCO引脚还可以通过GPIO复用功能来使用,实现其他功能,如输入捕获、输出比较等。

RCC里面开启

挨着的

在看就是可以输出了

我比较严谨,看到了这里的区别

原因是这个定时器时钟就是专门给定时器的

APB2分频器可选择1、2、4、8、16分频,其输出一路供APB2外设使用(PCLK2,最大频率72MHz),另一路送给定时器(Timer)1倍频器使用。

对的

该倍频器可选择1或者2倍频,时钟输出供定时器1使用。另外,APB2分频器还有一路输出供ADC分频器使用,分频后送给ADC模块使用。

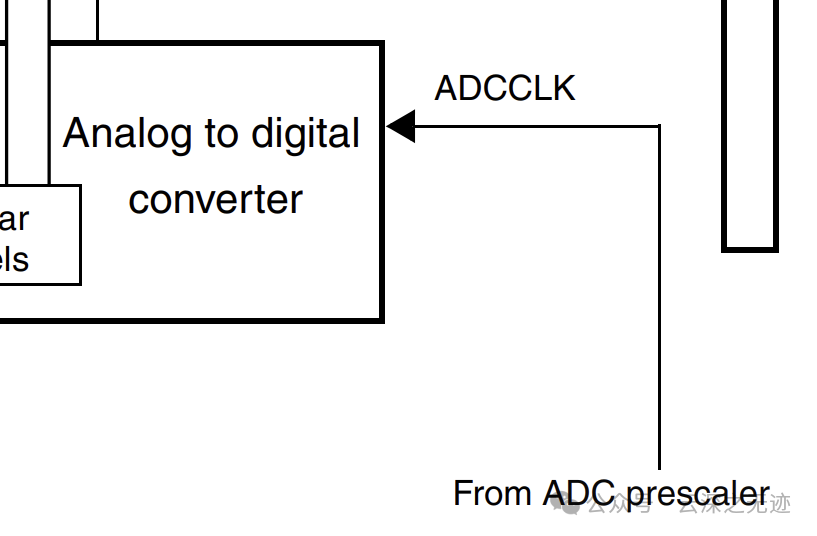

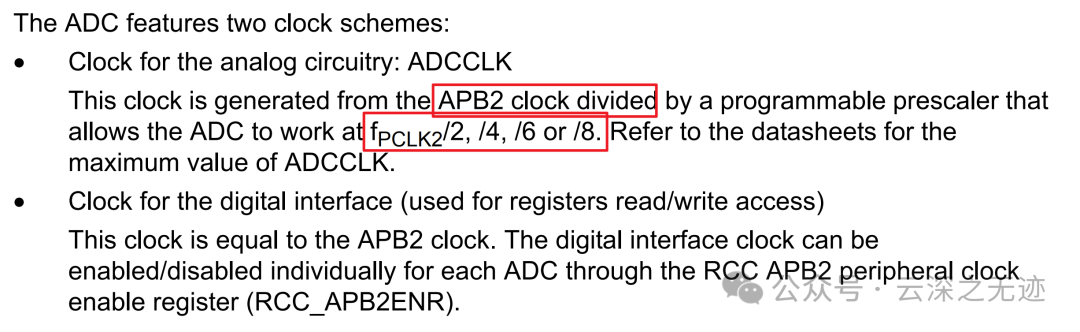

ADC分频器可选择为2、4、6、8分频。这个没有办法知道。

看图确实是有个分频的

ADC在APB2上面挂着

确实啊

也可以看中文版的

就是这个地方

本文参与 腾讯云自媒体同步曝光计划,分享自微信公众号。

原始发表:2025-02-05,如有侵权请联系 cloudcommunity@tencent.com 删除

评论

登录后参与评论

推荐阅读